## HIGH-SPEED 2K x 9 DUAL-PORT STATIC RAM WITH BUSY & INTERRUPT

IDT70121S/L IDT70125S/L

LEAD FINISH (SnPb) ARE IN EOL PROCESS - LAST TIME BUY EXPIRES JUNE 15, 2018

#### **Features**

- High-speed access

- Commercial: 25/35/55ns (max.)

- Industrial: 35ns (max.)

- Low-power operation

- IDT70121/70125S

Active: 675mW (typ.)

- Standby: 5mW (typ.)

- IDT70121/70125L

Active: 675mW (typ.)

Standby: 1mW (typ.)

- Fully asychronous operation from either port

- MASTER IDT70121 easily expands data bus width to 18 bits or more using SLAVE IDT70125 chip

- On-chip port arbitration logic (IDT70121 only)

- BUSY output flag on Master; BUSY input on Slave

- INT flag for port-to-port communication

- Battery backup operation—2V data retention

- TTL-compatible, signal 5V (±10%) power supply

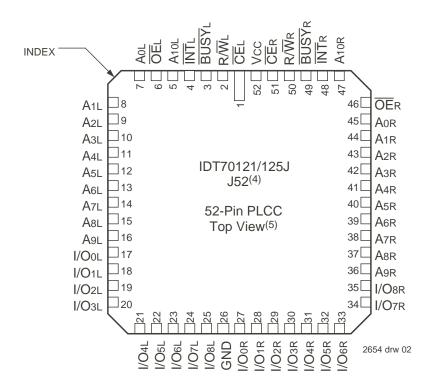

- Available in 52-pin PLCC

- Industrial temperature range (-40°C to +85°C) is available for selected speeds

- Green parts available, see ordering information

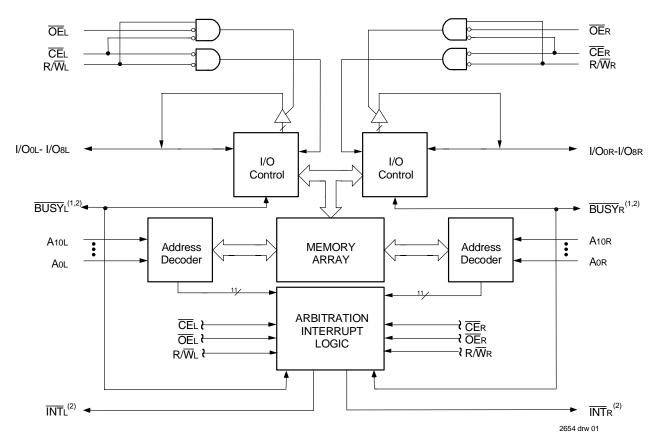

## Functional Block Diagram

#### NOTES:

- 70121 (MASTER): BUSY is non-tri-stated push-pull output. 70125 (SLAVE): BUSY is input.

- 2. INT is non-tri-stated push-pull output.

OCTOBER 2017

### Description

The IDT70121/IDT70125 are high-speed 2K x 9 Dual-Port Static RAMs. The IDT70121 is designed to be used as a stand-alone 9-bit Dual-Port RAM to gether with the IDT70125 "SLAVE" Dual-Port in 18-bit-or-more word width systems. Using the IDT MASTER/SLAVE Dual-Port RAM approach in 18-bit-or-wider memory system applications results in full-speed, error-free operation without the need for additional discrete logic.

Both devices provide two independent ports with separate control, address, and I/O pins that permit independent, asynchronous access for reads or writes to any location in memory. An automatic power-down

feature, controlled by  $\overline{\text{CE}}$ , permits the on-chip circuitry of each port to enter a very low standby power mode.

The IDT70121/IDT70125 utilizes a 9-bit wide data path to allow for Data/Control and parity bits at the user's option. This feature is especially useful in data communications applications where it is necessary to use a parity bit for transmission/reception error checking.

Fabricated using CMOS high-performance technology, these devices typically operate on only 675mW of power. Low-power (L) versions offer battery backup data retention capability with each port typically consuming 200µW from a 2V battery.

The IDT70121/IDT70125 devices are packaged in a 52-pin PLCC.

## Pin Configurations (1,2,3)

- 1. All Vcc pins must be connected to power supply.

- 2. All GND pins must be connected to ground supply.

- 3. Package body is approximately .75 in x .75 in x .17 in.

- 4. This package code is used to reference the package diagram.

- 5. This text does not indicate orientation of the actual part-marking.

## Absolute Maximum Ratings(1)

| Symbol               | Rating                                     | Commercial<br>& Industrial | Unit |

|----------------------|--------------------------------------------|----------------------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0               | V    |

| TBIAS                | Temperature<br>Under Bias                  | -55 to +125                | ۰C   |

| Tstg                 | Storage<br>Temperature                     | -65 to +150                | °C   |

| ЮИТ                  | DC Output<br>Current                       | 50                         | mA   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. VTERM must not exceed Vcc + 10% for more than 25% of the cycle time or 10ns maximum, and is limited to  $\leq$  20mA for the period of VTERM  $\geq$  Vcc + 10%.

## Maximum Operating Temperature and Supply Voltage<sup>(1)</sup>

| Grade      | Ambient<br>Temperature | GND | Vcc               |

|------------|------------------------|-----|-------------------|

| Commercial | 0°C to +70°C           | 0V  | 5.0V <u>+</u> 10% |

| Industrial | -40°C to +85°C         | 0V  | 5.0V <u>+</u> 10% |

#### NOTES:

1. This is the parameter Ta. This is the "instant on" case temperature.

## Recommended DC Operating Conditions

| Symbol | Parameter          | Min.                | Тур. | Max.   | Unit |

|--------|--------------------|---------------------|------|--------|------|

| Vcc    | Supply Voltage     | 4.5                 | 5.0  | 5.5    | ٧    |

| GND    | Ground             | 0                   | 0    | 0      | ٧    |

| VIH    | Input High Voltage | 2.2                 | _    | 6.0(2) | ٧    |

| VIL    | Input Low Voltage  | -0.5 <sup>(1)</sup> | _    | 0.8    | V    |

#### NOTES:

- 1.  $VIL \ge -1.5V$  for pulse width less than 10ns.

- 2. VTERM must not exceed Vcc + 10%.

## Capacitance (TA = +25°C, f = 1.0MHz)

| Symbol | Parameter          | Conditions <sup>(1)</sup> | Max. | Unit |

|--------|--------------------|---------------------------|------|------|

| CIN    | Input Capacitance  | VIN = 3dV                 | 9    | pF   |

| Соит   | Output Capacitance | Vout = 3dV                | 10   | pF   |

#### NOTE:

This parameter is determined by device characterization but is not production tested

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range ( $Vcc = 5.0V \pm 10\%$ )

|        |                                      |                                                             | 70121S<br>70125S |      | 70121L<br>70125L |      |      |

|--------|--------------------------------------|-------------------------------------------------------------|------------------|------|------------------|------|------|

| Symbol | Parameter                            | Test Conditions                                             | Min.             | Max. | Min.             | Max. | Unit |

| ILI    | Input Leakage Current <sup>(1)</sup> | Vcc = 5.5V, $VIN = 0V$ to $Vcc$                             | _                | 10   | _                | 5    | μΑ   |

| ILO    | Output Leakage Current               | $Vcc = 5.5V$ , $\overline{CE} = ViH$ , $Vout = 0V$ to $Vcc$ | _                | 10   | _                | 5    | μΑ   |

| Vol    | Output Low Voltage                   | lol = +4mA                                                  | _                | 0.4  | _                | 0.4  | V    |

| Vон    | Output High Voltage                  | IOH = -4mA                                                  | 2.4              | _    | 2.4              | _    | V    |

2654 tbl 02

#### NOTE:

1. At  $Vcc \le 2.0V$  leakages are undefined.

2654 tbl 05

2654 tbl 03

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range $^{(1,4)}$ (Vcc = 5V $\pm$ 10%)

|        |                                                        |                                                                                                                                    |        |        | 7012       | 1X25<br>5X25<br>Only | 7012<br>Co | 1X35<br>5X35<br>m'l<br>Ind |      |

|--------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------|----------------------|------------|----------------------------|------|

| Symbol | Parameter                                              | Test Condition                                                                                                                     | Versio | n      | Тур.       | Max.                 | Тур.       | Max.                       | Unit |

| Icc    | Dynamic Operating Current<br>(Both Ports Active)       | $\overline{CE} = VIL$ , Outputs Disabled<br>$f = fMAX^{(2)}$                                                                       | COM'L  | S<br>L | 135<br>135 | 260<br>220           | 135<br>135 | 250<br>210                 | mA   |

|        |                                                        | I = IIVIAX**                                                                                                                       | IND    | S<br>L | _          | -                    | 135<br>135 | 275<br>250                 |      |

| ISB1   | Standby Current<br>(Both Ports - TTL Level Inputs)     | $\overline{CE}$ "A" = $\overline{CE}$ "B" = VIH                                                                                    | COM'L  | S<br>L | 30<br>30   | 65<br>45             | 30<br>30   | 65<br>45                   | mA   |

|        |                                                        | $f = fMax^{(2)}$                                                                                                                   | IND    | S<br>L | _          |                      | 30<br>30   | 80<br>65                   |      |

| ISB2   | Standby Current<br>(One Port - TTL Level Inputs)       | CE'A" = VIL and CE'B" = VIH <sup>(5)</sup> Active Port Outputs Disabled, f=ftMAX <sup>(2)</sup>                                    | COM'L  | S<br>L | 80<br>80   | 175<br>145           | 80<br>80   | 165<br>135                 | mA   |

|        |                                                        | I=IVIAX **                                                                                                                         | IND    | S<br>L |            | 1 1                  | 80<br>80   | 190<br>165                 |      |

| ISB3   | Full Standby Current (Both Ports - CMOS Level Inputs)  | $\overline{CE}$ 'A" and $\overline{CE}$ 'B" $\geq$ VCC - 0.2V<br>VIN $\geq$ VCC - 0.2V or<br>VIN $\leq$ 0.2V, f = 0 <sup>(3)</sup> | COM'L  | S<br>L | 1.0<br>0.2 | 15<br>5              | 1.0<br>0.2 | 15<br>5                    | mA   |

|        |                                                        | $VIN \leq 0.2V, T = U^{ey}$                                                                                                        | IND    | S<br>L |            |                      | 1.0<br>0.2 | 15<br>5                    |      |

| ISB4   | Full Standby Current<br>(One Port - CMOS Level Inputs) | $\overline{CE}^*A^* \leq 0.2V$ and $\overline{CE}^*B^* \geq VCC - 0.2V^{(5)}$                                                      | COM'L  | S<br>L | 70<br>70   | 170<br>140           | 70<br>70   | 160<br>130                 | mA   |

|        |                                                        | $V_{IN} \ge \overline{V}_{CC} - 0.2V$ or $V_{IN} < 0.2V$<br>Active Port Outputs Disabled,<br>$f = f_{IM} x_{C}^{(2)}$              | IND    | S<br>L | _          |                      | 70<br>70   | 185<br>160                 |      |

2654 tbl 06a

|        |                                                        |                                                                                                                                                                               |        |        |            | 1X55<br>5X55<br>Only |      |

|--------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------|----------------------|------|

| Symbol | Parameter                                              | Test Condition                                                                                                                                                                | Versio | n      | Тур.       | Max.                 | Unit |

| Icc    | Dynamic Operating Current (Both Ports Active)          | CE = VIL, Outputs Disabled                                                                                                                                                    | COM'L  | S<br>L | 135<br>135 | 240<br>200           | mA   |

|        |                                                        | $f = fMAX^{(2)}$                                                                                                                                                              | IND    | S<br>L |            |                      |      |

| ISB1   | Standby Current<br>(Both Ports - TTL Level Inputs)     | $\overline{CE}$ "A" = $\overline{CE}$ "B" = VIH                                                                                                                               | COM'L  | S<br>L | 30<br>30   | 65<br>45             | mA   |

|        |                                                        | $f = fMAX^{(2)}$                                                                                                                                                              | IND    | S<br>L |            |                      |      |

| ISB2   | Standby Current<br>(One Port - TTL Level Inputs)       | CE"A" = VIL and CE"B" = VIH <sup>(5)</sup> Active Port Outputs Disabled, f=fMAX <sup>(2)</sup>                                                                                | COM'L  | S<br>L | 80<br>80   | 155<br>125           | mA   |

|        |                                                        | T=TMAX**/                                                                                                                                                                     | IND    | S<br>L | _          | _                    |      |

| ISB3   | Full Standby Current<br>(Both Ports - CMOS Level       | $\overline{CE}$ "A" and $\overline{CE}$ "B" $\geq$ VCC - 0.2V<br>VIN $\geq$ VCC - 0.2V or                                                                                     | COM'L  | S<br>L | 1.0<br>0.2 | 15<br>5              | mA   |

|        | Inputs)                                                | $VIN \le 0.2V, f = 0^{(3)}$                                                                                                                                                   | IND    | S<br>L |            |                      |      |

| ISB4   | Full Standby Current<br>(One Port - CMOS Level Inputs) | $\overline{CE}^*A^* \le 0.2V$ and $\overline{CE}^*B^* \ge VCC - 0.2V^{(5)}$                                                                                                   | COM'L  | S<br>L | 70<br>70   | 150<br>120           | mA   |

|        |                                                        | $\begin{array}{l} \text{VIN} \geq \overline{\text{VCC}} - 0.2 \text{V or VIN} \leq 0.2 \text{V} \\ \text{Active Port Outputs Disabled,} \\ f = f\text{MAX}^{(2)} \end{array}$ | IND    | S<br>L |            | _                    |      |

#### NOTES:

- 1. 'X' in part numbers indicates power rating (S or L).

- 2. At f = fmax, address and control lines (except Output Enable) are cycling at the maximum frequency read cycle of 1/trc, and using "AC TEST CONDITIONS" of input levels of GND to 3V.

- 3. f = 0 means no address or control lines change. Applies only to inputs at CMOS level standby.

- 4. Vcc=5V, Ta=+25°C for Typ, and is not production tested.

- 5. Port "A" may be either left or right port. Port "B" is opposite from port "A".

2654 tbl 06b

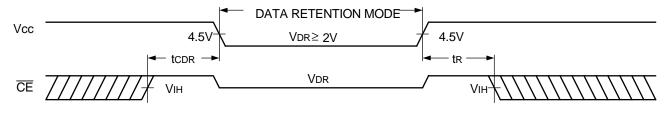

### Data Retention Characteristics (L Version Only)

| Symbol              | Parameter                            | Test Condition                                                    |        | Min.               | Typ. <sup>(1)</sup> | Max. | Unit |

|---------------------|--------------------------------------|-------------------------------------------------------------------|--------|--------------------|---------------------|------|------|

| <b>V</b> DR         | Vcc for Data Retention               |                                                                   |        | 2.0                | _                   | _    | V    |

| ICCDR               | Data Retention Current               | $Vcc = 2V$ , $\overline{CE} \ge Vcc - 0.2V$                       | IND.   | _                  | 100                 | 4000 | μΑ   |

| tcdr <sup>(3)</sup> | Chip Deselect to Data Retention Time | V <sub>IN</sub> ≥ V <sub>CC</sub> - 0.2V or V <sub>IN</sub> ≤ 0.2 | COM'L. | _                  | 100                 | 1500 |      |

| tR <sup>(3)</sup>   | Operation Recovery Time              |                                                                   |        | trc <sup>(2)</sup> | _                   | -    | V    |

2654 tbl 07

#### NOTES:

- 1. Vcc = 2V, TA = +25°C, and are not production tested.

- 2. tRC = Read Cycle Time.

- 3. This parameter is guaranteed but is not production tested.

### Data Retention Waveform

2654 drw 03

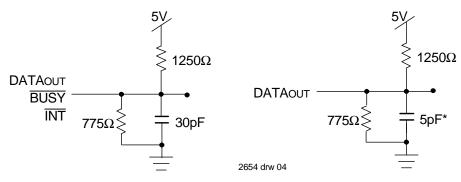

### **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V     |

|-------------------------------|-----------------|

| Input Rise/Fall Times         | 3ns             |

| Input Timing Reference Levels | 1.5V            |

| Output Reference Levels       | 1.5V            |

| Output Load                   | Figures 1 and 2 |

2654 tbl 08

Figure 1. AC Output Test Load

Figure 2. Output Test Load (For t.z, thz, twz, tow) \*Including scope and jig.

## AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(3)</sup>

| ·          |                                                | 70121X25<br>70125X25<br>Com'l Only |      | 70121X35<br>70125X35<br>Com'l<br>& Ind |      |      |

|------------|------------------------------------------------|------------------------------------|------|----------------------------------------|------|------|

| Symbol     | Parameter                                      | Min.                               | Max. | Min.                                   | Max. | Unit |

| READ CYCLE |                                                |                                    |      |                                        |      |      |

| trc        | Read Cycle Time                                | 25                                 |      | 35                                     | 1    | ns   |

| taa        | Address Access Time                            |                                    | 25   | _                                      | 35   | ns   |

| tace       | Chip Enable Access Time                        |                                    | 25   | _                                      | 35   | ns   |

| taoe       | Output Enable Access Time                      | _                                  | 12   | _                                      | 25   | ns   |

| toн        | Output Hold from Address Change                | 0                                  |      | 0                                      |      | ns   |

| tlz        | Output Low-Z Time <sup>(1,2)</sup>             | 0                                  | _    | 0                                      | _    | ns   |

| tHZ        | Output High-Z Time <sup>(1,2)</sup>            | _                                  | 10   | _                                      | 15   | ns   |

| tpu        | Chip Enable to Power Up Time <sup>(2)</sup>    | 0                                  | _    | 0                                      | _    | ns   |

| tpD        | Chip Disable to Power Down Time <sup>(2)</sup> | _                                  | 50   | _                                      | 50   | ns   |

2654 tbl 09a

|            |                                                | 7012 | 70121X55<br>70125X55<br>Com'l Only |      |

|------------|------------------------------------------------|------|------------------------------------|------|

| Symbol     | Parameter                                      | Min. | Max.                               | Unit |

| READ CYCLE |                                                |      |                                    |      |

| trc        | Read Cycle Time                                | 55   | _                                  | ns   |

| taa        | Address Access Time                            | _    | 55                                 | ns   |

| tace       | Chip Enable Access Time                        | _    | 55                                 | ns   |

| taoe       | Output Enable Access Time                      | _    | 35                                 | ns   |

| tон        | Output Hold from Address Change                | 0    | _                                  | ns   |

| tLZ        | Output Low-Z Time <sup>(1,2)</sup>             | 0    | _                                  | ns   |

| tHZ        | Output High-Z Time <sup>(1,2)</sup>            | _    | 30                                 | ns   |

| tpu        | Chip Enable to Power Up Time <sup>(2)</sup>    | 0    | _                                  | ns   |

| tpD        | Chip Disable to Power Down Time <sup>(2)</sup> |      | 50                                 | ns   |

2654 tbl 09b

- 1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

- This parameter guaranteed by device characterization, but is not production tested.

'X' in part numbers indicates power rating (S or L).

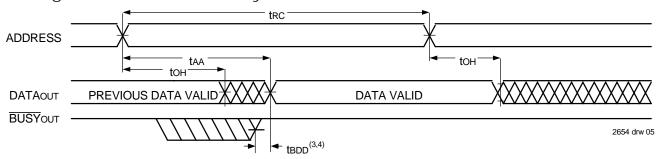

## Timing Waveform of Read Cycle No. 1, Either Side(1,2,4)

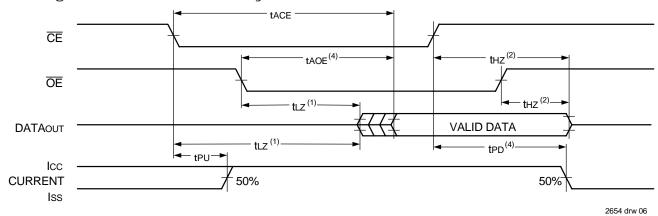

## Timing Waveform of Read Cycle No. 2, Either Side<sup>(5)</sup>

- 1. Timing depends on which signal is asserted last,  $\overline{\sf OE}$  or  $\overline{\sf CE}$ .

- 2. Timing depends on which signal is deaserted first,  $\overline{\text{OE}}$  or  $\overline{\text{CE}}.$

- 3. tBDD delay is required only in a case where the opposite port is completing a write operation to the same address location. For simultaneous read operations BUSY has no relationship to valid output data.

- 4. Start of valid data depends on which timing becomes effective last, tAOE, tACE, tAA, or tBDD.

- 5.  $R\overline{W} = V_{IH}$ ,  $\overline{CE} = V_{IL}$ , and  $\overline{OE} = V_{IL}$ , and the address is valid prior to other coincidental with  $\overline{CE}$  transition LOW.

## AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(4)</sup>

|             |                                                   | 70121X25<br>70125X25<br>Com'l Only |      | 70121X35<br>70125X35<br>Com'l<br>& Ind |      |      |

|-------------|---------------------------------------------------|------------------------------------|------|----------------------------------------|------|------|

| Symbol      | Parameter                                         | Min.                               | Max. | Min.                                   | Max. | Unit |

| WRITE CYCLE |                                                   |                                    |      |                                        |      |      |

| twc         | Write Cycle Time (4)                              | 25                                 | _    | 35                                     | _    | ns   |

| tew         | Chip Enable to End-of-Write                       | 20                                 | 1    | 30                                     | 1    | ns   |

| taw         | Address Valid to End-of-Write                     | 20                                 | _    | 30                                     | _    | ns   |

| tas         | Address Set-up Time                               | 0                                  | 1    | 0                                      |      | ns   |

| twp         | Write Pulse Width <sup>(6)</sup>                  | 20                                 |      | 30                                     |      | ns   |

| twr         | Write Recovery Time                               | 0                                  | 1    | 0                                      |      | ns   |

| tow         | Data Valid to End-of-Write                        | 12                                 | I    | 20                                     | I    | ns   |

| tHZ         | Output High-Z Time <sup>(1,2,3)</sup>             | _                                  | 10   |                                        | 15   | ns   |

| tон         | Data Hold Time <sup>(5)</sup>                     | 0                                  |      | 0                                      | _    | ns   |

| twz         | Write Enable to Output in High-Z <sup>(1,3)</sup> |                                    | 10   | _                                      | 15   | ns   |

| tow         | Output Active from End-of-Write (1,2,3,5)         | 0                                  | _    | 0                                      | _    | ns   |

2654 tbl 10a

|            |                                                      | 7012<br>7012<br>Com'l |      |    |

|------------|------------------------------------------------------|-----------------------|------|----|

| Symbol     | Parameter                                            | Min.                  | Unit |    |

| WRITE CYCL | E                                                    |                       |      |    |

| twc        | Write Cycle Time <sup>(4)</sup>                      | 55                    | _    | ns |

| tew        | Chip Enable to End-of-Write                          | 40                    | _    | ns |

| taw        | Address Valid to End-of-Write                        | 40                    | _    | ns |

| tas        | Address Set-up Time                                  | 0                     | _    | ns |

| twp        | Write Pulse Width <sup>(6)</sup>                     | 40                    | _    | ns |

| twr        | Write Recovery Time                                  | 0                     | _    | ns |

| tow        | Data Valid to End-of-Write                           | 20                    | _    | ns |

| tHZ        | Output High-Z Time <sup>(1,2,3)</sup>                | _                     | 30   | ns |

| tон        | Data Hold Time <sup>(5)</sup>                        | 0                     | _    | ns |

| twz        | Write Enable to Output in High-Z <sup>(1,3)</sup>    |                       | 30   | ns |

| tow        | Output Active from End-of-Write <sup>(1,2,3,5)</sup> | 0                     | _    | ns |

\_ \_ 2654 tbl 10b

- 1. Transition is measured 0mV from Low or High-impedance voltage with Output Test Load (Figure 2).

- 2. This parameter guaranteed by device characterization, but is not production tested.

- 3. For MASTER/SLAVE combination, two = tbaa + twp, since R/W = VIL must occur after tbaa.

- 4. 'X' in part numbers indicates power rating (S or L).

- 5. The specified toH must be met by the device supplying write date to the RAM under all operating conditions. Although toH and tow values will vary over voltage and temperature. The actual toH will always be smaller than the actual tow.

- 6. If  $\overline{OE}$  is LOW during a R/ $\overline{W}$  controlled write cycle, the write pulse width must be the larger of twp or (twz + tow) to allow the I/O drivers to turn off data to be placed on the bus for the required tow. If  $\overline{OE}$  is HIGH during a R/ $\overline{W}$  controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twp.

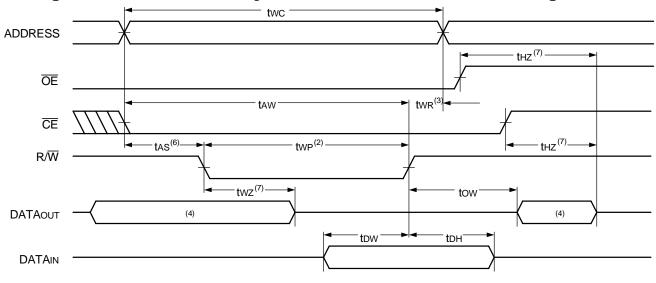

## Timing Waveform of Write Cycle No. 1, R/W Controlled Timing (1,5,8)

2654 drw 07

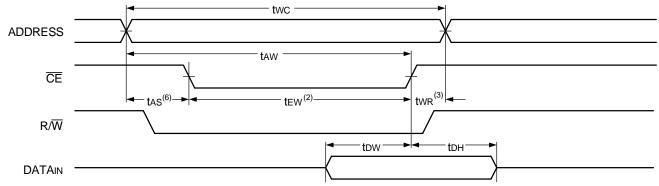

## Timing Waveform of Write Cycle No. 2, **CE** Controlled Timing<sup>(1,5)</sup>

2654 drw 08

- 1.  $R/\overline{W}$  or  $\overline{CE}$  must be HIGH during all address transitions.

- 2. A write occurs during the overlap (tew or twp) of a  $\overline{CE}$  = V<sub>IL</sub> and a R/ $\overline{W}$  = V<sub>IL</sub>

- 3. twn is measured from the earlier of  $\overline{\text{CE}}$  or  $R/\overline{W}$  going HIGH to the end of the write cycle.

- 4. During this period, the I/O pins are in the output state and input signals must not be applied.

- 5. If the CE LOW transition occurs simultaneously with or after the RW LOW transition, the outputs remain in the High-impedance state.

- 6. Timing depends on which enable signal (CE or R/W) is asserted last.

- 7. This parameter is determined be device characterization, but is not production tested. Transition is measured 0mV from steady state with the Output Test Load (Figure 2).

- 8. If  $\overline{OE}$  is LOW during a R $\overline{W}$  controlled write cycle, the write pulse width must be the larger of twp or (twz + tow) to allow the I/O drivers to turn off data to be placed on the bus for the required tow. If  $\overline{OE}$  is HIGH during a R $\overline{W}$  controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twp.

# IDT70121/IDT70125 High-Speed 2K x 9 Dual-Port Static RAM with Busy & Interrupt

## AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(6)</sup>

|             |                                                    | 70121X25<br>70125X25<br>Com'l Only |      | 70121X35<br>70125X35<br>Com'l<br>& Ind |    |    |  |

|-------------|----------------------------------------------------|------------------------------------|------|----------------------------------------|----|----|--|

| Symbol      | Parameter                                          | Max.                               | Min. | Max. Unit                              |    |    |  |

| BUSY TIMING | G (For MASTER IDT70121)                            |                                    |      |                                        |    |    |  |

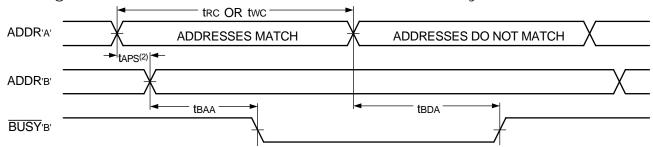

| tbaa        | BUSY Access Time from Address                      | _                                  | 20   | _                                      | 20 | ns |  |

| tbda        | BUSY Disable Time from Address                     |                                    | 20   | _                                      | 20 | ns |  |

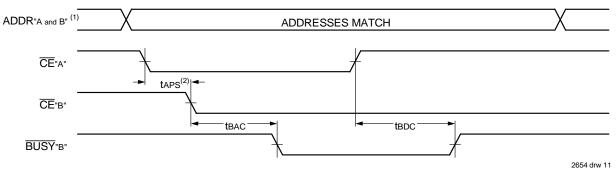

| tBAC        | BUSY Access Time from Chip Enable                  | _                                  | 20   | _                                      | 20 | ns |  |

| tBDC        | BUSY Disable Time from Chip Enable                 |                                    | 20   | _                                      | 20 | ns |  |

| twdd        | Write Pulse to Data Delay <sup>(1)</sup>           |                                    | 50   |                                        | 60 |    |  |

| todo        | Write Data Valid to Read Data Delay <sup>(1)</sup> |                                    | 35   |                                        | 45 |    |  |

| taps        | Arbitration Priority Set-up Time <sup>(2)</sup>    | 5                                  |      | 5                                      | _  | ns |  |

| tBDD        | BUSY Disable to Valid Data <sup>(3)</sup>          |                                    | 30   | _                                      | 30 | ns |  |

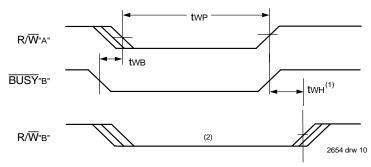

| twн         | Write Hold After BUSY <sup>(5)</sup>               | 15                                 | _    | 20                                     |    | ns |  |

| BUSY INPUT  | TIMING (For SLAVE IDT70125)                        |                                    |      |                                        |    |    |  |

| twB         | Write to BUSY Input <sup>(4)</sup>                 | 0                                  |      | 0                                      |    | ns |  |

| twн         | Write Hold After BUSY <sup>(5)</sup>               | 15                                 |      | 20                                     |    | ns |  |

| twdd        | Write Pulse to Data Delay <sup>(1)</sup>           | _                                  | 50   | _                                      | 60 | ns |  |

| todo        | Write Data Valid to Read Data Delay <sup>(1)</sup> |                                    | 35   | _                                      | 45 | ns |  |

2654 tbl 11a

|                    |                                                    | 7012<br>7012<br>Com' |      |      |  |

|--------------------|----------------------------------------------------|----------------------|------|------|--|

| Symbol             | Parameter                                          | Min.                 | Max. | Unit |  |

| <b>BUSY</b> TIMING |                                                    |                      |      |      |  |

| tbaa               | BUSY Access Time from Address                      | _                    | 30   | ns   |  |

| tbda               | BUSY Disable Time from Address                     | _                    | 30   | ns   |  |

| tBAC               | BUSY Access Time from Chip Enable                  | _                    | 30   | ns   |  |

| tBDC               | BUSY Disable Time from Chip Enable                 | _                    | 30   | ns   |  |

| twdd               | Write Pulse to Data Delay <sup>(1)</sup>           |                      | 80   |      |  |

| todo               | Write Data Valid to Read Data Delay <sup>(1)</sup> |                      | 65   |      |  |

| taps               | Arbitration Priority Set-up Time <sup>(2)</sup>    | 5                    |      | ns   |  |

| tbdd               | BUSY Disable to Valid Data <sup>(3)</sup>          | _                    | 45   | ns   |  |

| twн                | Write Hold After BUSY <sup>(5)</sup>               | 20                   |      | ns   |  |

| BUSY INPUT         | TIMING (For SLAVE IDT 70125)                       |                      |      |      |  |

| twB                | Write to BUSY Input <sup>(4)</sup>                 | 0                    |      | ns   |  |

| twn                | Write Hold After BUSY <sup>(5)</sup>               | 20                   |      | ns   |  |

| twdd               | Write Pulse to Data Delay <sup>(1)</sup>           | _                    | 80   | ns   |  |

| todo               | Write Data Valid to Read Data Delay <sup>(1)</sup> | _                    | 65   | ns   |  |

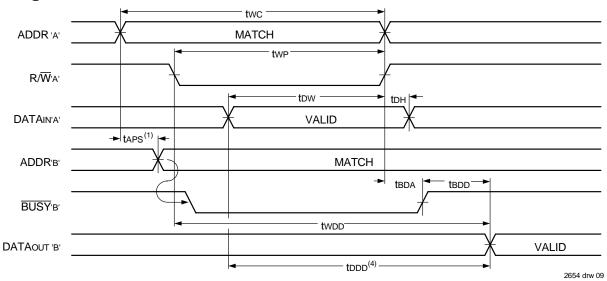

- 1. Port-to-port delay through RAM cells from writing port to reading port, refer to "Timing Waveform of Write with Port-to-Port Read and BUSY.

- 2. To ensure that the earlier of the two ports wins.

- 3. tbdd is a calculated parameter and is the greater of 0, twdd twp (actual) or tddd tow (actual).

- 4. To ensure that a write cycle is inhibited on port 'B' during contention on port 'A'...

- 5. To ensure that a write cycle is completed on port 'B' after contention on port 'A'.

- 6. 'X' in part numbers indicates power rating (S or L).

## Timing Waveform of Write with Port-to-Port Read and **BUSY**(1,2,3)

#### NOTES:

- To ensure that the earlier of the two ports wins. taps is ignored for Slave (IDT70125).

- 2.  $\overline{CE}L = \overline{CE}R = VIL$

- 3.  $\overline{OE} = V_{IL}$  for the reading port.

- 4. All timing is the same for the left and right ports. Port 'A' may be either the left or right port. Port "B" is opposite from port "A".

## Timing Waveform of Write with **BUSY**(3)

#### NOTES:

- 1. twh must be met for both BUSY input (slave) and output (master).

- 2.  $\overline{\text{BUSY}}$  is asserted on port 'B' blocking R/ $\overline{\text{W}}$ 'B', until  $\overline{\text{BUSY}}$ 'B' goes HIGH.

- 3. All timing is the same for left and right ports. Port"A" may be either left or right port. Port "B" is the opposite from port "A".

## Timing Waveform of **BUSY** Arbitration Controlled by **CE** Timing<sup>(1)</sup>

- 1. All timing is the same for left and right ports. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

- If taps is not satisfied, the BUSY will be asserted on one side or the other, but there is no guarantee on which side BUSY will be asserted (70121 only).

Timing Waveform of **BUSY** Arbritration Controlled by Address<sup>(1)</sup>

NOTES: 1. All timing is the same for left and right ports. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

2. If taps is not satisfied, the BUSY will be asserted on one side or the other, but there is no quarantee on which side BUSY will be asserted (70121 only).

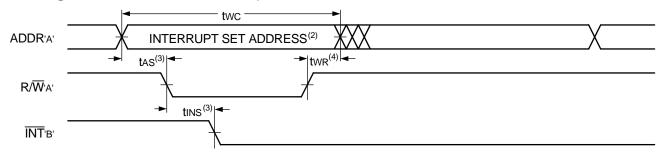

## AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(1)</sup>

|             |                      | 70121X25<br>70125X25<br>Com'l Only |      | 70121X35<br>70125X35<br>Com'l<br>& Ind |    |    |  |

|-------------|----------------------|------------------------------------|------|----------------------------------------|----|----|--|

| Symbol      | Parameter            | Min.                               | Max. | Unit                                   |    |    |  |

| INTERRUPT 1 | TIMING               |                                    |      |                                        |    |    |  |

| tas         | Address Set-up Time  | 0                                  | _    | 0                                      | _  | ns |  |

| twr         | Write Recovery Time  | 0                                  | _    | 0                                      | _  | ns |  |

| tins        | Interrupt Set Time   | _                                  | 25   | _                                      | 35 | ns |  |

| tinr        | Interrupt Reset Time |                                    | 25   | _                                      | 35 | ns |  |

2654 tbl 12a

2654 drw 12

|             |                      | 7012<br>7012<br>Com' |    |    |  |  |  |

|-------------|----------------------|----------------------|----|----|--|--|--|

| Symbol      | Parameter Min. Max   |                      |    |    |  |  |  |

| INTERRUPT 1 | TIMING               |                      |    |    |  |  |  |

| tas         | Address Set-up Time  | 0                    | _  | ns |  |  |  |

| twr         | Write Recovery Time  | 0                    |    | ns |  |  |  |

| tins        | Interrupt Set Time   | _                    | 45 | ns |  |  |  |

| tinr        | Interrupt Reset Time | _                    | 45 | ns |  |  |  |

2654 tbl 12b

1. 'X' in part numbers indicates power rating (S or L).

## Timing Waveform of Interrupt Mode<sup>(1)</sup>

NOTES:.

2654 drw 13

- 1. All timing is the same for left and right ports. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

- 2. See Interupt Truth Table.

- 3. Timing depends on which enable signal ( $\overline{\text{CE}}$  or  $R/\overline{W}$ ) is asserted last.

- 4. Timing depends on which enable signal  $(\overline{CE} \text{ or } R/\overline{W})$  is de-asserted first.

#### Truth Tables

## Truth Table I. Non-Contention Read/Write Control<sup>(4)</sup>

|     | Left or | Right Port <sup>(1)</sup> | ı                |                                                                      |

|-----|---------|---------------------------|------------------|----------------------------------------------------------------------|

| R/W | CE      | Œ                         | D <sub>0-8</sub> | Function                                                             |

| Х   | Н       | Х                         | Z                | Port Disable and in Power-Down Mode, ISB2 or ISB4                    |

| Х   | Н       | Χ                         | Z                | $\overline{CE}R = \overline{CE}L = H$ , Power-DownMode, ISB1 or ISB3 |

| L   | L       | Х                         | DATAIN           | Data on Port Written Into Memory <sup>(2)</sup>                      |

| Н   | L       | L                         | DATAout          | Data in Memory Output on Port <sup>(3)</sup>                         |

| Н   | L       | Н                         | Z                | High-Impedance Outputs                                               |

NOTES: 2654 tbl 13

- 1.  $A0L A10L \neq A0R A10R$ .

- 2. If  $\overline{\text{BUSY}} = L$ , data is not written.

- 3. If  $\overline{\text{BUSY}}$  = L, data may not be valid, see two and too timing.

- 4. 'H' = VIH, 'L' = VIL, 'X' = DON'T CARE, 'Z' = HIGH IMPEDANCE

## Truth Table II. Interrupt Flag<sup>(1,4)</sup>

|               |             | Left Port |          |                  | Right Port |     |             |          |                  |                       |

|---------------|-------------|-----------|----------|------------------|------------|-----|-------------|----------|------------------|-----------------------|

| R/ <b>W</b> L | <u>C</u> E∟ | ŌĒL       | A10L-A0L | ĪNTL             | R/W̄R      | CER | <b>ŌĒ</b> R | A10R-A0R | Ī <b>NT</b> R    | Function              |

| L             | L           | Х         | 7FF      | Х                | Х          | Х   | Х           | Х        | L <sup>(2)</sup> | Set Right INTR Flag   |

| Х             | Х           | Х         | Х        | Х                | Х          | L   | L           | 7FF      | H <sup>(3)</sup> | Reset Right INTR Flag |

| Х             | Х           | Х         | Х        | L <sup>(3)</sup> | L          | L   | Х           | 7FE      | Х                | Set Left INTL Flag    |

| Х             | L           | L         | 7FE      | H <sup>(2)</sup> | Х          | Х   | Х           | Χ        | Х                | Reset Left INTL Flag  |

NOTES:

2654 tbl 14

- 1. Assumes  $\overline{BUSY}L = \overline{BUSY}R = VIH$

- 2. If  $BUSYL = V_{IL}$ , then No Change.

- 3. If BUSYR = VIL, then No Change.

- 4. 'H' = HIGH,' L' = LOW,' X' = DON'T CARE

## **Functional Description**

The IDT70121/125 provides two ports with separate control, address and I/O pins that permit independent access for reads or writes to any location in memory. The IDT70121/125 has an automatic power down feature controlled by  $\overline{\text{CE}}$ . The  $\overline{\text{CE}}$  controls on-chip power down circuitry that permits the respective port to go into a standby mode when not selected ( $\overline{\text{CE}}$  HIGH). When a port is enabled, access to the entire memory array is permitted.

### Interrupts

If the user chooses the interrupt function, a memory location (mail box or message center) is assigned to each port. The left port interrupt flag ( $\overline{\text{INTL}}$ ) is asserted when the right port writes to memory location 7FE (HEX), where a write is defined as the  $\overline{\text{CE}}$  =  $R/\overline{\text{W}}$  = VIL per Truth Table II. The left port clears the interrupt by access address location 7FE access when  $\overline{\text{CE}}$  =  $\overline{\text{OE}}$ R = VIL,  $R/\overline{\text{W}}$  is a "don't care". Likewise, the right port interrupt flag (INTR) is asserted when the left port writes to memory location 7FF (HEX) and to clear the interrupt flag (INTR), the right port must access the memory location 7FF. The message (9 bits) at 7FE or 7FF is user-defined, since it is an addressable SRAM location. If the interrupt function is not used, address locations 7FE and 7FF are not used as mail boxes, but as part of the random access memory. Refer to Table II for the interrupt operation.

## **Busy Logic**

Busy Logic provides a hardware indication that both ports of the RAM have accessed the same location at the same time. It also allows one of the two accesses to proceed and signals the other side that the RAM is "busy". The  $\overline{\text{BUSY}}$  pin can then be used to stall the access until the operation on the other side is completed. If a write operation has been attempted from the side that receives a  $\overline{\text{BUSY}}$  indication, the write signal is gated internally to prevent the write from proceeding.

The use of  $\overline{BUSY}$  logic is not required or desirable for all applications. In some cases it may be useful to logically OR the  $\overline{BUSY}$  outputs together and use any  $\overline{BUSY}$  indication as an interrupt source to flag the event of an illegal or illogical operation. If the write inhibit function of  $\overline{BUSY}$  logic is not desirable, the  $\overline{BUSY}$  logic can be disabled by using the IDT70125 (SLAVE). In the IDT70125, the  $\overline{BUSY}$  pin operates solely as a write inhibit input pin. Normal operation can be programmed by tying the  $\overline{BUSY}$  pins HIGH. Once in slave mode the  $\overline{BUSY}$  pin operates solely as a write inhibit input pin. If desired, unintended write operations can be prevented to a port by tying the  $\overline{BUSY}$  pin for that port LOW.

The BUSY outputs on the IDT70121/125 RAM in master mode, are push-pull type outputs and do not require pull up resistors to operate. If these RAMs are being expanded in depth, then the BUSY indication for the resulting array requires the use of an external AND gate.

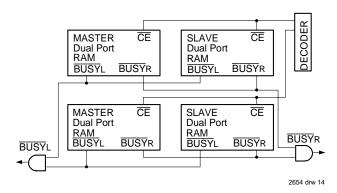

## Width Expansion with Busy Logic Master/Slave Arrays

When expanding an IDT70121/125 RAM array in width while using  $\overline{\text{BUSY}}$  logic, one master part is used to decide which side of the RAM array will receive a  $\overline{\text{BUSY}}$  indication, and to output that indication. Any number of slaves to be addressed in the same address range as the master use the  $\overline{\text{BUSY}}$  signal as a write inhibit signal. Thus on the IDT70121 RAM the  $\overline{\text{BUSY}}$  pin is an output of the part, and the BUSY pin is an input of the IDT70125 as shown in Figure 3.

If two or more master parts were used when expanding in width, a split decision could result with one master indicating  $\overline{\text{BUSY}}$  on one side of the array and another master indicating  $\overline{\text{BUSY}}$  on one other side of the array. This would inhibit the write operations from one port for part of a word and

Figure 3. Busy and chip enable routing for both width and depth expansion with 70121 (Master) and 70125 (Slave) RAMs.

inhibit the write operations from the other port for the other part of the word.

The  $\overline{BUSY}$  arbitration, on a master, is based on the chip enable and address signals only. It ignores whether an access is a read or write. In a master/slave array, both address and chip enable must be valid long enough for a  $\overline{BUSY}$  flag to be output from the master before the actual write pulse can be initiated with either the  $R\overline{W}$  signal or the byte enables. Failure to observe this timing can result in a glitched internal write inhibit signal and corrupted data in the slave.

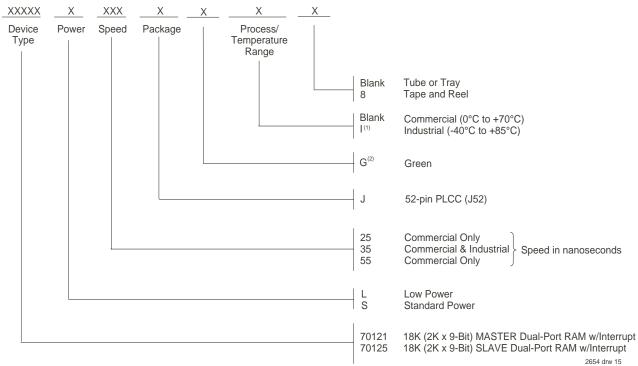

## Ordering Information

#### NOTES:

- 1. Industrial temperature: for other speeds, packages and powers contact your sales office.

- Green parts available. For specific speeds, packages and powers contact your local sales office LEAD FINISH (SnPb) parts are in EOL process. Product Discontinuation Notice - PDN# SP-17-02.

## Datasheet Document History

01/06/99: Initiated datasheet document history

Converted to newformat

Cosmetic and typographical corrections

Pages 2 and 3 Added additional notes to pin configurations

06/03/99: Changed drawing format Corrected DSC number

05/28/04: Page 3 Changed storage temperature parameter from -55 to +125 to -65 to +150

Clarified TA parameter footnote

Page 4 DC Electrical parameters–changed test condition wording from "open" to "disabled"

$\begin{array}{ll} \text{Page 9} & \text{Changed} \pm 500 \text{mV} \text{ to } 0 \text{mV} \text{ in notes} \\ \text{Page 2} & \text{Added date revision for pin configuration} \end{array}$

Page 4, 6, 8, 10&12 Added Industrial temp to column headings for 35ns speed to DC and AC Electrical Characteristics

Page 4 Removed Industrial temp from 25, 45 & 55ns speeds from DC Electrical Characteristics

Page 3, 4, 6, 8, 10 & 12 Removed Industrial temp footnote from all tables

Page 10 Corrected error in AC BUSY timing tables changing 71V33 to 70121 and changing 71V43 to 70125

Page 15 Added Industrial temp offering to 35ns ordering information

Page 1 & 15 Replaced old TM logo with new TM logo

Page 6 Footnote reference 5 removed from AC Electrical Characteristics READ table

Page 1 Changed wording of footnote 1 from "INT is totem-pole output" to "INT is non-tr-stated push-pull output"

## Datasheet Document History (cont'd)

|           | Page 5         | Updated AC Test Conditions Input Rise/Fall Times from 5ns to 3ns                         |

|-----------|----------------|------------------------------------------------------------------------------------------|

| 04/05/06: | Page 1         | Added green availability to features                                                     |

|           | Page 15        | Added green indicator to ordering information                                            |

| 10/21/08: | Page 15        | Removed "IDT" from orderable part number                                                 |

| 08/05/14: | Page 1         | Added green availability to Features                                                     |

|           | Page 15        | Added green indicator to Ordering Information                                            |

|           | Page 2 &15     | The package code for the J52-1 changed to J52 to match standard package code             |

|           | Page 15        | Added Tape and Reel to Ordering Information                                              |

| 08/27/14: | Page 1         | Removed 45ns commercial speed grade from Features High-speed access                      |

|           | _              | information                                                                              |

|           | Page 1-16      | Removed 45ns commercial speed grade throughout the datasheet to correct a discrepancy in |

|           |                | IDT's product catalog                                                                    |

|           | Page 4         | Specifically including the DC Chars table                                                |

|           | Page 6,8,10&12 | Specifically including the AC Chars tables                                               |

|           | Page 15        | Removed 45ns commercial speed grade from the Ordering Information                        |

| 10/10/17: | •              | Product Discontinuation Notice - PDN# SP-17-02                                           |

|           |                | Last time buy expires June 15, 2018                                                      |

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## IDT (Integrated Device Technology):

70121L55J8

70125S55J8

70121L25JG

70125L25J

70125L25J

70125L35J

70121S25J8

70125L25JG8

70121L25JG8

70125L25J8

70121L25J

70121L35J8

70125S35J8

70121L55J

70121L35J

70125S35J

70121S35J

70121S35J8

70121S35JI

70121S35JI