## AS3415/AS3435

# **Integrated Active Noise Cancelling Solution with Bypass Feature**

#### **General Description**

The AS3415/35 are speaker drivers with Ambient Noise Cancelling function for headsets, headphones or ear pieces. They are intended to improve quality of e.g. music listening, a phone conversation etc. by reducing background ambient noise.

The fully analog implementation allows the lowest power consumption, lowest system BOM cost and most natural received voice enhancement otherwise difficult to achieve with DSP implementations. The device is designed to be easily applied to existing architectures.

An internal OTP-ROM can be optionally used to store the microphones gain calibration settings. The AS3415/35 can be used in different configurations for best trade-off of noise cancellation, required filtering functions and mechanical designs.

The simpler feed-forward topology is used to effectively reduce frequencies typically up to 2-3 kHz. The feed-back topology with either 1 or 2 filtering stages has its strengths especially at very low frequencies. The typical bandwidth for a feed-back system is from 20Hz up to 1 kHz which is lower than the feed-forward systems.

The filter loop for both systems is determined by measurements, for each specific headset individually, and depends very much on mechanical designs. The gain and phase compensation filter network is implemented with cheap resistors and capacitors for lowest system costs.

#### **Key Benefits & Features**

The benefits and features of AS3415/35, Integrated Active Noise Cancelling Solution with Bypass Feature are listed below:

Figure 1: Added Value of Using AS3415/35

| Benefits                          | Features                              |

|-----------------------------------|---------------------------------------|

| All ANC Topologies                | Feed Forward, Feed Back and Hybrid    |

| No mechanical audio bypass switch | Integrated depletion mode transistors |

| Music EQ functionality            | Ultra flexible low power EQ circuit   |

| Longest play time                 | 10mW @1.5V stereo ANC; <1μA quiescent |

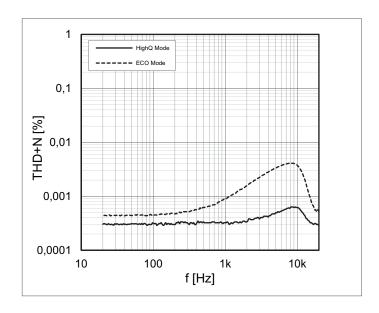

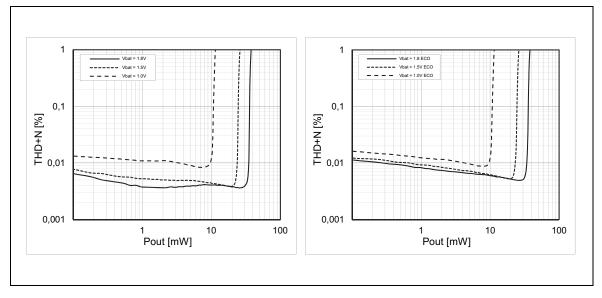

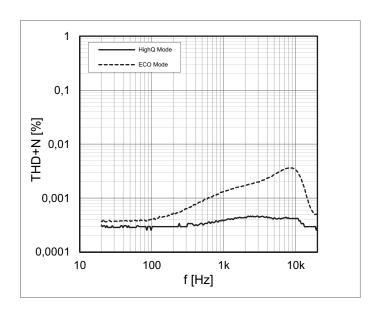

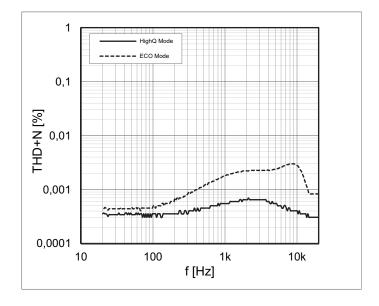

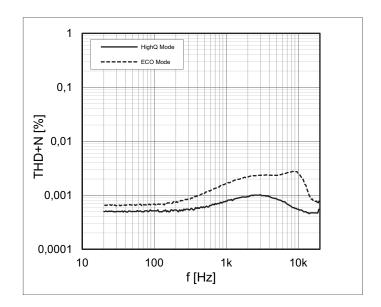

| Highest audio quality             | 2x24mW, 0.1% THD+N @ 32Ω, 1.5V supply |

ams Datasheet, Confidential: 2013-Sep [1-10]

| Benefits                                                      | Features                                                                                                  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

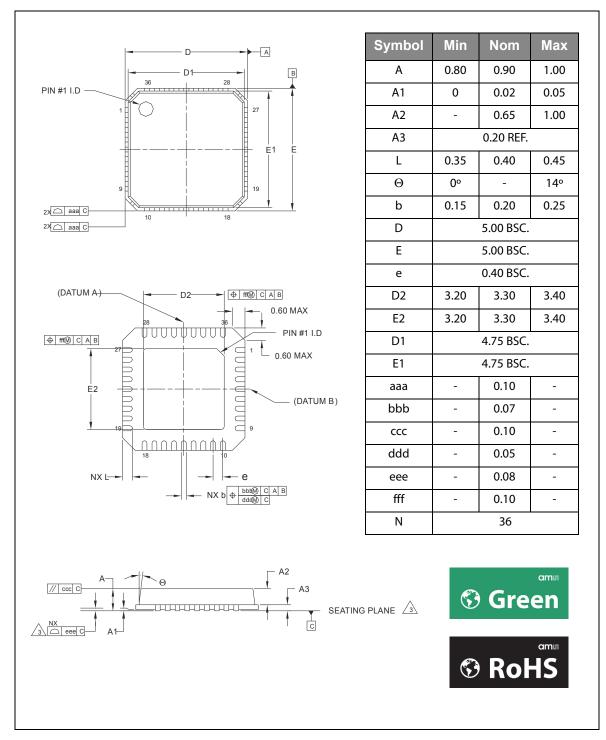

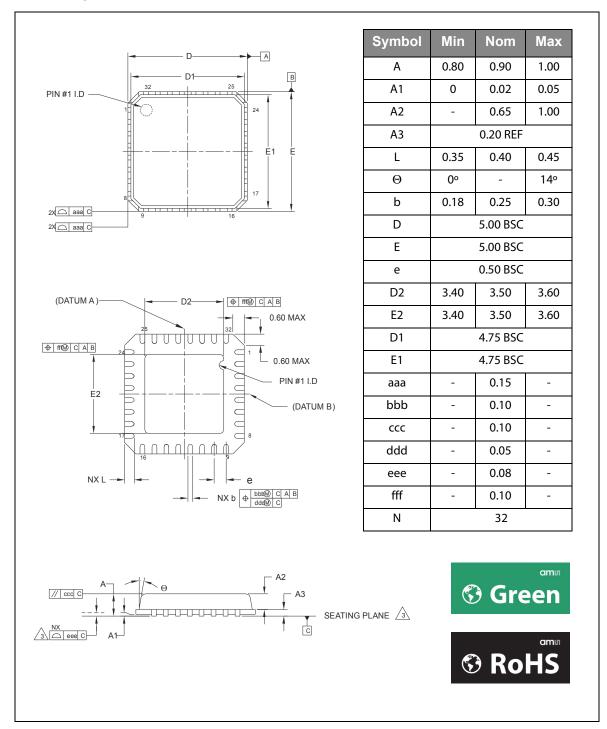

| Smallest package                                              | Two different packages available:  • AS3415 QFN32 [5x5mm] 0.5mm pitch  • AS3435 QFN36 [5x5mm] 0.4mm pitch |

| Low battery indication                                        | LED driver with selectable driving strength                                                               |

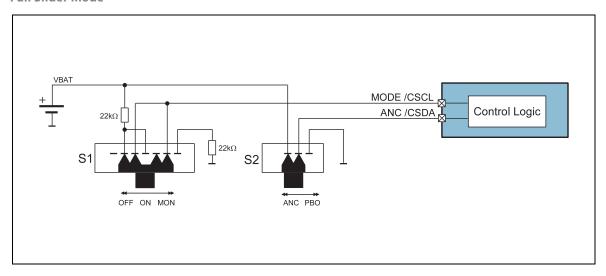

| Different control interface options                           | Push Button-, Slide switch- or I <sup>2</sup> C control interface                                         |

| Highly innovative production trimming interface               | OTP production trimming via audio interface                                                               |

| Active hearing mode with or without ANC and optional voice EQ | Monitor mode function                                                                                     |

#### **Applications**

The devices are ideal for:

- Ear pieces

- Headsets

- · Hands-Free Kits

- Mobile Phones

- Voice Communicating Devices

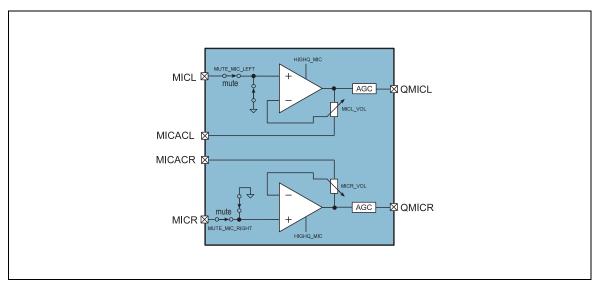

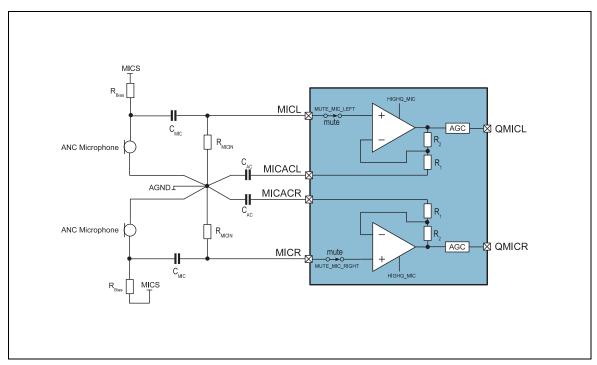

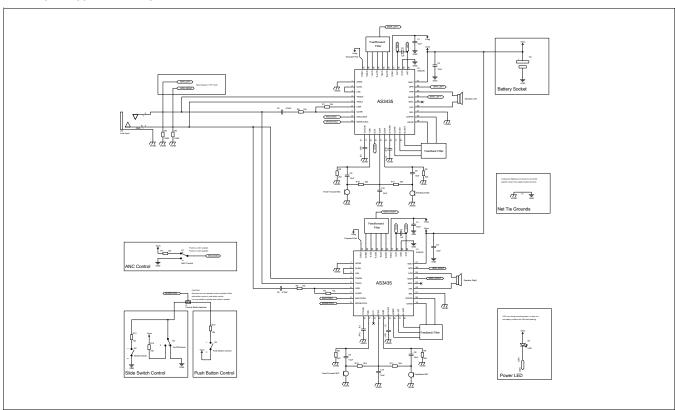

#### **Block Diagram**

The functional blocks of AS3415/35 for reference are shown below:

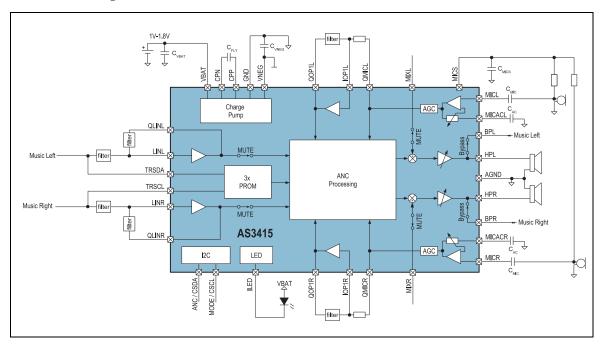

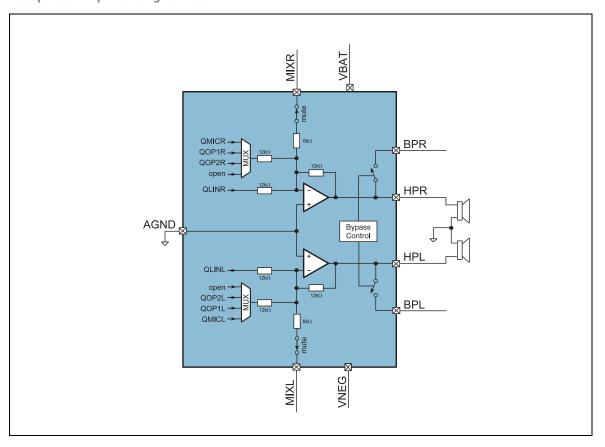

Figure 2: AS3415 Block Diagram

**AS3415 Block Diagram:** This figure shows the block diagram of the AS3415 with all relevant system components.

AS3415/AS3435 – 2

ams Datasheet, Confidential: 2013-Sep [1-10]

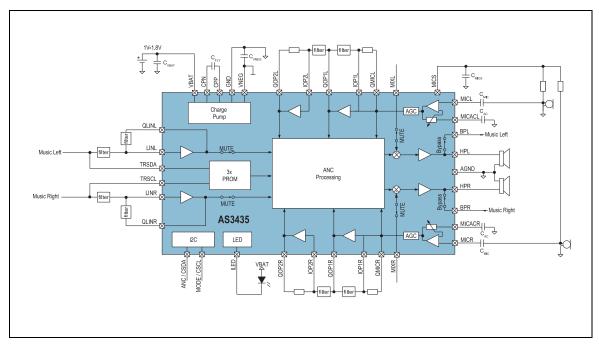

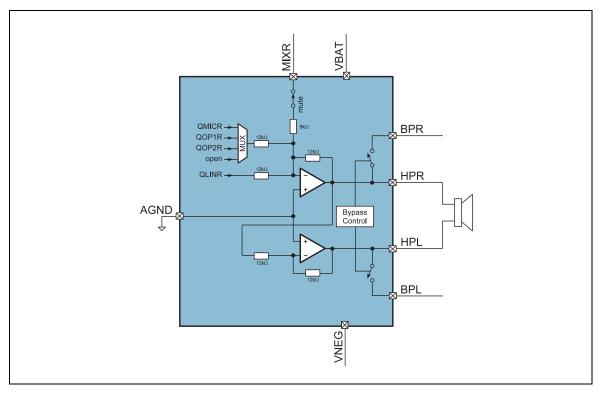

Figure 3: AS3435 Block Diagram

**AS3435 Block Diagram:** This figure shows the block diagram of the AS3435 with all relevant system components.

#### **Pin Assignment**

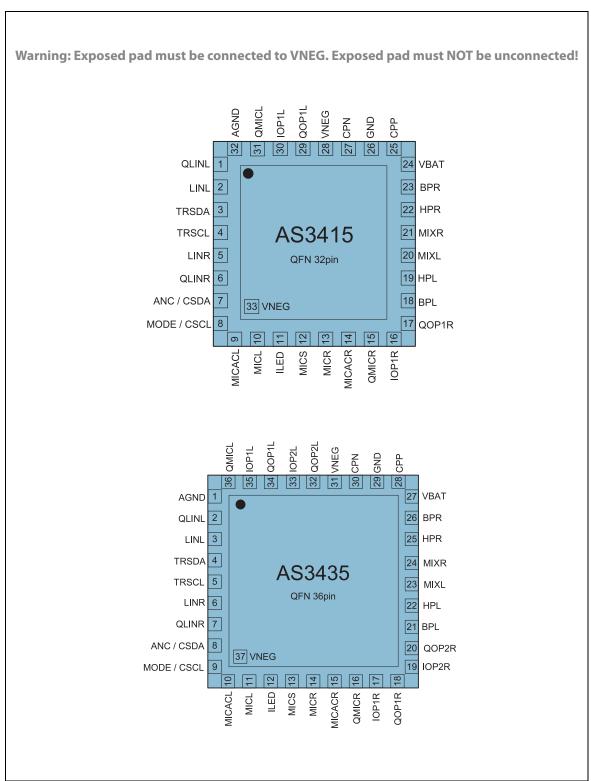

The AS3415 and AS3435 pin assignments are described below.

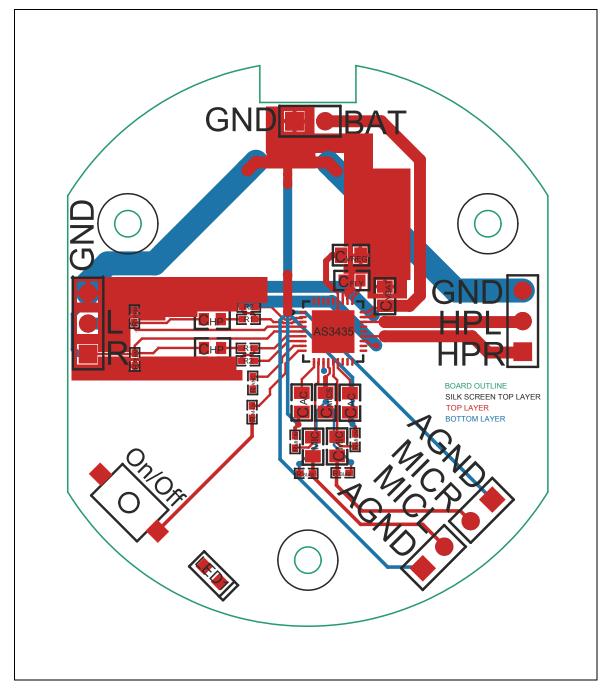

Figure 4: Pin Assignments

**Pin Assignments:** Shows the pin assignment of the AS3415 and AS3435 (Top View).

### **Pin Description**

The following figure shows the pin description for AS3415/35.

Figure 5: Pin Description

| Pin Name    | Pin Nu | umber  | Din Type | Description                                                                                                           |

|-------------|--------|--------|----------|-----------------------------------------------------------------------------------------------------------------------|

| PIII Naiile | AS3435 | AS3415 | Pin Type | Description                                                                                                           |

| AGND        | 1      | 32     | ANA OUT  | Analog reference ground. Do not connect this pin to power or digital ground plane.                                    |

| QLINL       | 2      | 1      | ANA OUT  | Line input EQ gain stage output left channel.                                                                         |

| LINL        | 3      | 2      | ANA IN   | Line input EQ left channel.                                                                                           |

| TRSDA       | 4      | 3      | ANA IN   | Clock input for production trimming. Can be connected to LINL pin to enable production trimming via 3.5mm audio jack. |

| TRSCL       | 5      | 4      | ANA IN   | Data input for production trimming. Can be connected to LINR pin to enable production trimming via 3.5mm audio jack.  |

| LINR        | 6      | 5      | ANA IN   | Line input EQ right channel.                                                                                          |

| QLINR       | 7      | 6      | ANA IN   | Line input EQ gain stage output right channel.                                                                        |

| ANC / CSDA  | 8      | 7      | DIG IN   | Serial interface data for I <sup>2</sup> C interface and ANC control to enable/disable ANC.                           |

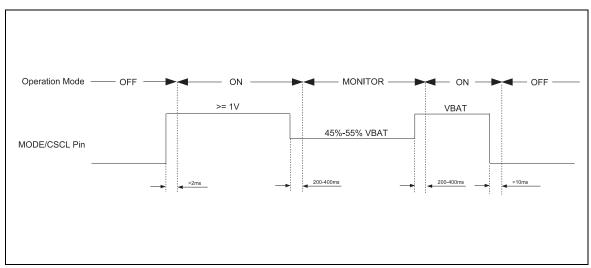

| MODE / CSCL | 9      | 8      | DIG IN   | Serial Interface Clock for I <sup>2</sup> C interface and control pin for power up/down and Monitor mode.             |

| MICACL      | 10     | 9      | ANA OUT  | Microphone preamplifier AC coupling ground terminal. This pin requires a 10μF capacitor connected to AGND pin.        |

| MICL        | 11     | 10     | ANA IN   | ANC microphone input left channel.                                                                                    |

| ILED        | 12     | 11     | ANA IN   | Current sink input for on-indication LED.                                                                             |

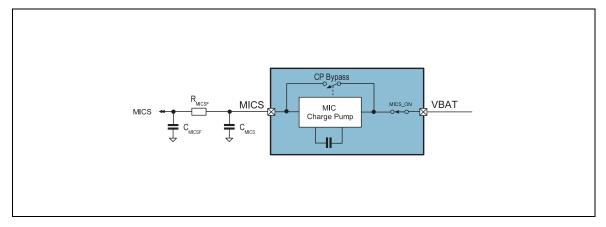

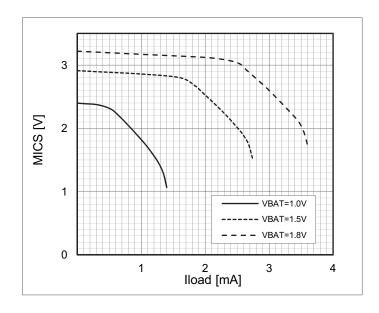

| MICS        | 13     | 12     | SUP OUT  | Microphone Supply output. This pin needs an output blocking capacitor with 10μF.                                      |

| MICR        | 14     | 13     | ANA IN   | ANC microphone preamplifier input right channel.                                                                      |

| MICACR      | 15     | 14     | ANA OUT  | Microphone preamplifier AC coupling ground terminal. This pin requires a 10μF capacitor connected to AGND pin.        |

| QMICR       | 16     | 15     | ANA OUT  | ANC microphone preamplifier output right channel.                                                                     |

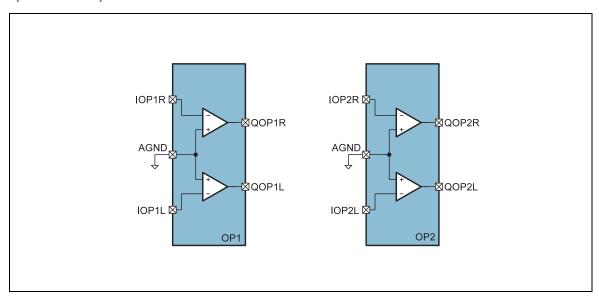

| IOP1R       | 17     | 16     | ANA IN   | ANC filter OpAmp1 input right channel.                                                                                |

| QOP1R       | 18     | 17     | ANA OUT  | ANC filter OpAmp1 output right channel.                                                                               |

| Pin Name  | Pin Nu | umber  | Pin Type  | Description                                                                                    |

|-----------|--------|--------|-----------|------------------------------------------------------------------------------------------------|

| Pili Name | AS3435 | AS3415 | Pili Type | Description                                                                                    |

| IOP2R     | 19     | -      | ANA IN    | ANC Filter OpAmp2 input right channel.                                                         |

| QOP2R     | 20     | -      | ANA OUT   | ANC filter OpAmp2 output right channel.                                                        |

| BPL       | 21     | 18     | ANA IN    | Left audio bypass terminal input.                                                              |

| HPL       | 22     | 19     | ANA OUT   | Headphone amplifier output left channel                                                        |

| MIXL      | 23     | 20     | ANA IN    | Headphone amplifier external summation input terminal left channel.                            |

| MIXR      | 24     | 21     | ANA IN    | Headphone amplifier external summation input terminal right channel.                           |

| HPR       | 25     | 22     | ANA OUT   | Headphone amplifier output right channel                                                       |

| BPR       | 26     | 23     | ANA OUT   | Right audio bypass terminal input.                                                             |

| VBAT      | 27     | 24     | SUP IN    | Positive supply terminal of IC.                                                                |

| СРР       | 28     | 25     | ANA OUT   | V <sub>NEG</sub> charge pump flying capacitor positive terminal.                               |

| GND       | 29     | 26     | GND       | V <sub>NEG</sub> charge pump ground terminal.                                                  |

| CPN       | 30     | 27     | ANA OUT   | V <sub>NEG</sub> charge pump flying capacitor negative terminal.                               |

| VNEG      | 31     | 28     | SUP OUT   | V <sub>NEG</sub> charge pump output. This pin must be connected to exposed pad of QFN package. |

| QOP2L     | 32     | -      | ANA OUT   | ANC Filter OpAmp2 output left channel.                                                         |

| IOP2L     | 33     | -      | ANA IN    | ANC Filter OpAmp2 input left channel.                                                          |

| QOP1L     | 34     | 29     | ANA IN    | Filter OpAmp1 output left channel.                                                             |

| IOP1L     | 35     | 30     | ANA OUT   | Filter OpAmp1 input left channel.                                                              |

| QMICL     | 36     | 31     | SUP IN    | ANC microphone preamplifier output left channel.                                               |

| VNEG      | 37     | 33     | SUP IN    | Exposed Pad: Must be connected to VNEG pin 31(AS3435) or 28(AS3415).                           |

**Pin Description:** This table shows a detailed pin description of the AS3415 and AS3435.

#### **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 6: Absolute Maximum Ratings

| Parameter                         | Min                   | Max                   | Units                                     | Comments                                                                                                                                                          |  |

|-----------------------------------|-----------------------|-----------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reference Ground                  |                       |                       |                                           | Defined as in GND                                                                                                                                                 |  |

| Supply terminals                  | -0.5                  | 2.0                   | V                                         | Applicable for pin VBAT                                                                                                                                           |  |

| Ground terminals                  | -0.5                  | 0.5                   | V                                         | Applicable for pin AGND                                                                                                                                           |  |

| Negative terminals                | -2.0                  | 0.5                   | V                                         | Applicable for pins VNEG                                                                                                                                          |  |

| Charge Pump pins                  | V <sub>NEG</sub> -0.5 | V <sub>BAT</sub> +0.5 | V                                         | Applicable for pins CPN and CPP                                                                                                                                   |  |

| Headphone pins                    | VSS-0.5               | V <sub>BAT</sub> +0.5 | V                                         | Applicable for pins HPR and HPL                                                                                                                                   |  |

| Analog pins                       | VSS-0.5               | V <sub>BAT</sub> +0.5 | V                                         | Applicable for pins LINL, LINR,<br>MICL/R, HPR, HPL, QMICL/R,<br>QLINL/R, IOPx, QOPx, CPP, CPN,<br>TRSCL, TRSDA, MICACL, MICACR,<br>MIXR, MIXL, BPL, BPR and ILED |  |

| Control Pins                      | VSS-0.5               | 5                     | V                                         | Applicable for pins MICS,<br>ANC/CSDA, MODE/CSCL                                                                                                                  |  |

| Other Pins                        | VSS-0.5               | 5                     | V                                         | Applicable for pin MICS                                                                                                                                           |  |

| Input Current (latch-up immunity) | -100                  | 100                   | mA                                        | Norm: JEDEC 17                                                                                                                                                    |  |

| Co                                | ntinuous Pov          | ver Dissipati         | on (T <sub>A</sub> = +7                   | /0°C)                                                                                                                                                             |  |

| Continuous Power Dissipation      | -                     | 200                   | mW                                        | PT <sup>(1)</sup> for QFN32/36 package                                                                                                                            |  |

| Electrostatic Discharge           |                       |                       |                                           |                                                                                                                                                                   |  |

| Electrostatic Discharge HBM       |                       | ± 2                   | kV                                        | Norm: JEDEC JESD22-A114C                                                                                                                                          |  |

| Tem                               | perature Rai          | nges and Sto          | rage Cond                                 | itions                                                                                                                                                            |  |

| Junction Temperature              |                       | +85                   | ۰C                                        |                                                                                                                                                                   |  |

| Storage Temperature Range         | -55                   | +125                  | °C                                        |                                                                                                                                                                   |  |

| Humidity non-condensing           | 5                     | 85                    | %                                         |                                                                                                                                                                   |  |

| Moisture Sensitive Level          | 3                     | 3                     | Represents a max. floor life time of 168h |                                                                                                                                                                   |  |

| Parameter                | Min | Max | Units | Comments                                                                                                                                                                                                     |

|--------------------------|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package Body Temperature |     | 260 | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/JEDEC J-STD-020"Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices". |

#### Note(s) and/or Footnote(s):

<sup>1.</sup> Depending on actual PCB layout and PCB used

#### **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

$V_{BAT}$  = 1.0V to 1.8V,  $T_A$  = -20°C to +85°C. Typical values are at  $V_{BAT}$  = 1.5V,  $T_A$  = +25°C, unless otherwise specified.

Figure 7: Electrical Characteristics

| TA Ambient Temperature Range       Supply Voltages         Supply Voltages         GND       Reference Ground       0       0       0       V         V <sub>BAT</sub> Battery Supply Voltage       Normal operation       1.0       1.8       V         V <sub>NEG</sub> Charge Pump Voltage       -1.8       -0.7       V         Voltage Pump Voltage       To achieve good performance, the negative supply terminals should be connected to a low impedance ground plane.       -0.1       0.1       V         VMICS       Microphone Supply Voltage       MICS       0       3.7       V         VANALOG       Analog Pins       MICS       0       3.7       V         VANALOG       Analog Pins       MICSACL, MICACR, LINR, LINL, MIXL, MIXL, MIXL, MIXL, MIXR, HPR, HPL, QMICL, QMICR, QLINL, QLINR, IOPx, QOPx, BPL, BPR       V_NEG       V_BAT       V         VCONTROL       Control Pins       MODE/CSCL, ANC/CSDA       V_NEG       3.7       V         VLED       ILED current source       ILED       VSS       V_BAT       V         VCP       Charge Pump pins       CPN, CPP       V_NEG       V_BAT       V         VMIC       Microphone Inputs       MICL and MICR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Symbol                                                                                      | Parameter             | Conditions                                                              | Min              | Тур | Max              | Unit |   |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------|------------------|-----|------------------|------|---|--|

| GND Reference Ground  VBAT Battery Supply Voltage  Normal operation  Two wire interface operation  1.0 1.8 V  Neg Charge Pump Voltage  To achieve good performance, the negative supply terminals should be connected to a low impedance ground plane.  Other pins  VMICS Microphone Supply Voltage  MICS 0 3.7 V  VANALOG Analog Pins MICACL, MICACR,LINR, LINL, MIXL, MIXR, HPR, HPL, QMICL, QMICR, QLINL, QLINR, IOPX, QOPX, BPL, BPR  VCONTROL Control Pins MODE/CSCL, ANC/CSDA VNEG 3.7 V  VLED ILED current source ILED VSS VBAT V  VTRIM Application Trim Pins TRSCL and TRSDA VSS VBAT V  VMIC Microphone Inputs MICL and MICR VSS VBAT V  VBAT VBAT V  VBAT V  VBAT V  VBAT V  VANALOG Microphone Inputs MICL and MICR VSS VBAT V  Leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T <sub>A</sub>                                                                              |                       |                                                                         | -20              |     | +85              | °C   |   |  |

| V <sub>BAT</sub> Battery Supply Voltage       Normal operation       1.0       1.8       V         V <sub>NEG</sub> Charge Pump Voltage       -1.8       -1.8       -0.7       V         V <sub>DELTA</sub> Difference of Ground Supplies GND, AGND       To achieve good performance, the negative supply terminals should be connected to a low impedance ground plane.       -0.1       0.1       V         V <sub>MICS</sub> Microphone Supply Voltage       MICS       0       3.7       V         V <sub>ANALOG</sub> Analog Pins       MICACL, MICACR, LINR, LINL, MIXL, MIXL, MIXR, HPR, HPL, QMICL, QMICR, QLINL, QLINR, IOPx, QOPx, BPL, BPR       V <sub>NEG</sub> V <sub>BAT</sub> V         V <sub>CONTROL</sub> Control Pins       MODE/CSCL, ANC/CSDA       V <sub>NEG</sub> 3.7       V         V <sub>LED</sub> ILED current source       ILED       VSS       V <sub>BAT</sub> V         V <sub>CP</sub> Charge Pump pins       CPN, CPP       V <sub>NEG</sub> V <sub>BAT</sub> V         V <sub>TRIM</sub> Application Trim Pins       TRSCL and TRSDA       V <sub>NEG</sub> V <sub>BAT</sub> V         V <sub>MIC</sub> Microphone Inputs       MICL and MICR       VSS       V <sub>BAT</sub> V         I <sub>leak</sub> Leakage current       V <sub>BAT</sub> 0.8V       20       µA <td></td> <td colspan="8">Supply Voltages</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             | Supply Voltages       |                                                                         |                  |     |                  |      |   |  |

| VBAT       Battery Supply Voltage       Two wire interface operation       1.4       1.8       V         VNEG       Charge Pump Voltage       -1.8       -0.7       V          To achieve good performance, the negative supply terminals should be connected to a low impedance ground plane.       -0.1       0.1       V          Microphone Supply voltage       MICS       0       3.7       V          MICS       VNEG       VNEG       VBAT       V <td rowspile<="" td=""><td>GND</td><td>Reference Ground</td><td></td><td>0</td><td></td><td>0</td><td>V</td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <td>GND</td> <td>Reference Ground</td> <td></td> <td>0</td> <td></td> <td>0</td> <td>V</td> | GND                   | Reference Ground                                                        |                  | 0   |                  | 0    | V |  |

| Voltage       Two wire interface operation       1.4       1.8       V         VNEG       Charge Pump Voltage       -1.8       -0.7       V         VDifference of Ground Supplies GND, AGND       To achieve good performance, the negative supply terminals should be connected to a low impedance ground plane.       -0.1       0.1       V         VMICS       Microphone Supply Voltage       MICS       0       3.7       V         VANALOG       Analog Pins       MICACL, MICACR, LINR, LINL, MIXL, MIXL, MIXR, HPR, HPL, QMICL, QMICR, QLINL, QLINR, IOPx, QOPx, BPL, BPR       V_NEG       V_BAT       V         VCONTROL       Control Pins       MODE/CSCL, ANC/CSDA       V_NEG       3.7       V         VLED       ILED current source       ILED       VSS       V_BAT       V         V_P       Charge Pump pins       CPN, CPP       V_NEG       V_BAT       V         VTRIM       Application Trim Pins       TRSCL and TRSDA       V_NEG       V_BAT       V         VMIC       Microphone Inputs       MICL and MICR       VSS       V_BAT       V         Umage of the properties of the p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>2.47</sub>                                                                           |                       | Normal operation                                                        | 1.0              |     | 1.8              | V    |   |  |

| Voltage  Voltage  Voltage  Difference of Ground Supplies GND, AGND  Other pins  Other pins  Vancs  Vanalog Pins  Microphone Supply Voltage  MICS  MICACL, MICACR, LINR, LINL, MIXL, MIXL, QLINL, OLINL, OLINLA, O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ▼BAI                                                                                        | Voltage               | Two wire interface operation                                            | 1.4              |     | 1.8              | V    |   |  |

| VDELTA       Difference of Ground Supplies GND, AGND       negative supply terminals should be connected to a low impedance ground plane.       -0.1       0.1       V         Other pins         V <sub>MICS</sub> Microphone Supply Voltage       MICS       0       3.7       V         V <sub>ANALOG</sub> Analog Pins       MICACL, MICACR, LINR, LINL, MIXL, MIXL, MIXL, MIXR, HPL, QMICL, QMICR, QLINL, QLINR, IOPX, QOPX, BPL, BPR       V <sub>NEG</sub> V <sub>BAT</sub> V         V <sub>CONTROL</sub> Control Pins       MODE/CSCL, ANC/CSDA       V <sub>NEG</sub> 3.7       V         V <sub>LED</sub> ILED current source       ILED       VSS       V <sub>BAT</sub> V         V <sub>TRIM</sub> Application Trim Pins       CPN, CPP       V <sub>NEG</sub> V <sub>NEG</sub> V <sub>BAT</sub> V         V <sub>MIC</sub> Microphone Inputs       MICL and MICR       VSS       V <sub>BAT</sub> V         I <sub>leak</sub> Leakage current       V <sub>BAT</sub> <0.8V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>NEG</sub>                                                                            |                       |                                                                         | -1.8             |     | -0.7             | V    |   |  |

| V <sub>MICS</sub> Microphone Supply Voltage       MICS       0       3.7       V         V <sub>ANALOG</sub> Analog Pins       MICACL, MICACR, LINR, LINL, MIXL, MIXL, MIXL, MIXR, HPR, HPL, QMICL, QMICR, QLINL, QLINL, QLINR, IOPX, QOPX, BPL, BPR       V <sub>NEG</sub> V <sub>BAT</sub> V         V <sub>CONTROL</sub> Control Pins       MODE/CSCL, ANC/CSDA       V <sub>NEG</sub> 3.7       V         V <sub>LED</sub> ILED current source       ILED       VSS       V <sub>BAT</sub> V         V <sub>CP</sub> Charge Pump pins       CPN, CPP       V <sub>NEG</sub> V <sub>BAT</sub> V         V <sub>TRIM</sub> Application Trim Pins       TRSCL and TRSDA       V <sub>NEG</sub> -0.3 or -1.8 or -1.8 or -1.8       V         V <sub>MIC</sub> Microphone Inputs       MICL and MICR       VSS       V <sub>BAT</sub> V         I <sub>leak</sub> Leakage current       V <sub>BAT</sub> <0.8V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>DELTA</sub>                                                                          | Supplies              | negative supply terminals should be connected to a low impedance ground | -0.1             |     | 0.1              | V    |   |  |

| Vanalog Voltage  Vanalog Pins  MICACL, MICACR, LINL, MIXL, MIXL, MIXR, HPR, HPL, QMICL, QMICR, QLINL, QLINL, QLINL, QLINR, IOPx, QOPx, BPL, BPR  VCONTROL Control Pins  MODE/CSCL, ANC/CSDA  VNEG  3.7  V  VLED  ILED current source  ILED  VSS  VBAT  V  VCP  Charge Pump pins  CPN, CPP  VNEG  VNEG  VNEG  VBAT  V  V  V  VBAT  V  V  V  V  V  V  V  V  V  V  V  V  V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             | I                     | Other pins                                                              | I                |     | l                |      |   |  |

| VANALOG       Analog Pins       MIXR, HPR, HPL, QMICL, QMICR, QLINL, QLINL, QLINR, IOPx, QOPx, BPR       VNEG       VBAT       V         VCONTROL       Control Pins       MODE/CSCL, ANC/CSDA       VNEG       3.7       V         VLED       ILED current source       ILED       VSS       VBAT       V         VCP       Charge Pump pins       CPN, CPP       VNEG       VBAT       V         VTRIM       Application Trim Pins       TRSCL and TRSDA       VNEG -0.3 or -1.8       VBAT +0.5 or 1.8       V         VMIC       Microphone Inputs       MICL and MICR       VSS       VBAT       V         Ileak       Leakage current       VBAT       V       20       μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>MICS</sub>                                                                           |                       | MICS                                                                    | 0                |     | 3.7              | V    |   |  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>ANALOG</sub>                                                                         | Analog Pins           | MIXR, HPR, HPL, QMICL, QMICR, QLINL,                                    | V <sub>NEG</sub> |     | V <sub>BAT</sub> | V    |   |  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CONTROL</sub>                                                                        | Control Pins          | MODE/CSCL, ANC/CSDA                                                     | V <sub>NEG</sub> |     | 3.7              | V    |   |  |

| $V_{TRIM}  \text{Application Trim Pins}  TRSCL \text{ and TRSDA} \qquad \begin{array}{c} V_{NEG} \\ -0.3 \\ \text{or} \\ -1.8 \end{array} \qquad \begin{array}{c} V_{BAT} \\ +0.5 \\ \text{or} \ 1.8 \end{array} \qquad V$ $V_{MIC}  \text{Microphone Inputs}  \text{MICL and MICR} \qquad \qquad VSS \qquad V_{BAT}  V$ $I_{leak}  Leakage \text{ current} \qquad \begin{array}{c} V_{BAT} < 0.8V \\ \end{array} \qquad \qquad \begin{array}{c}$ | V <sub>LED</sub>                                                                            | ILED current source   | ILED                                                                    | VSS              |     | V <sub>BAT</sub> | V    |   |  |

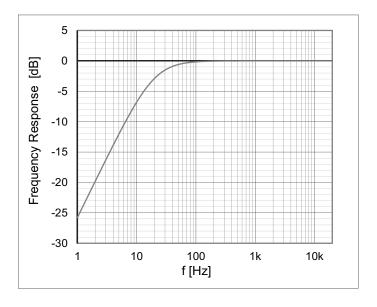

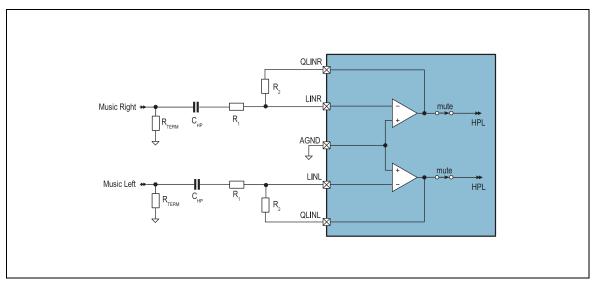

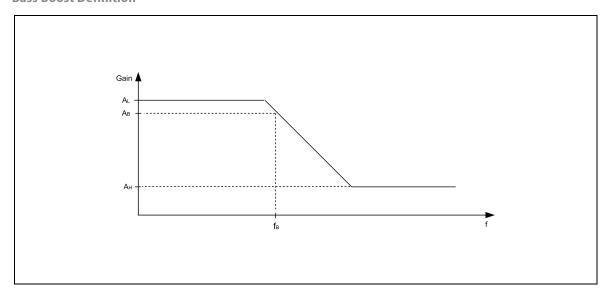

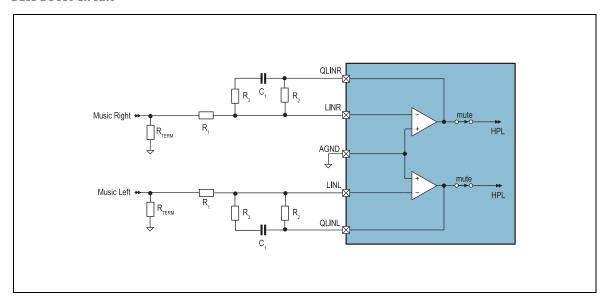

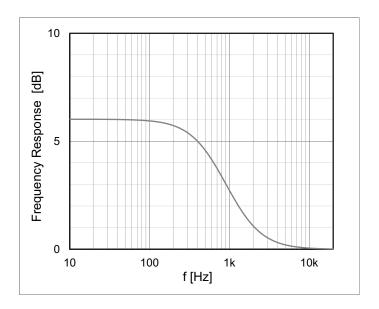

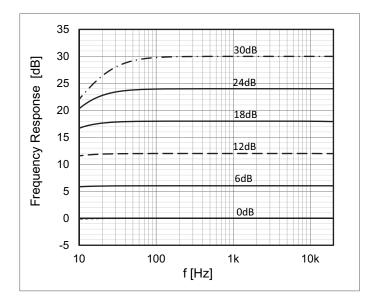

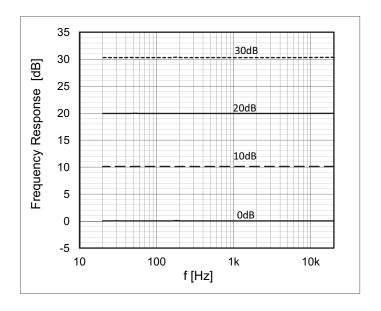

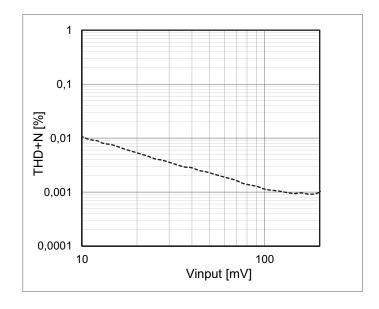

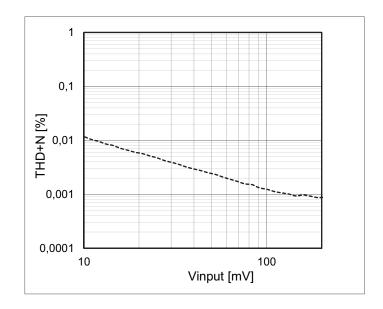

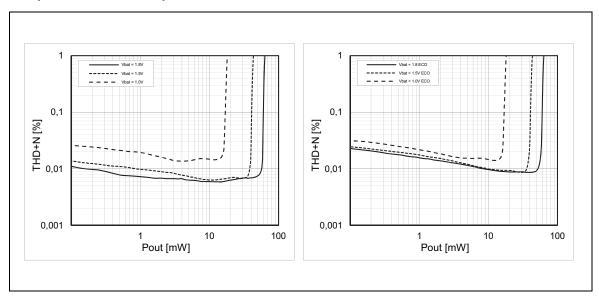

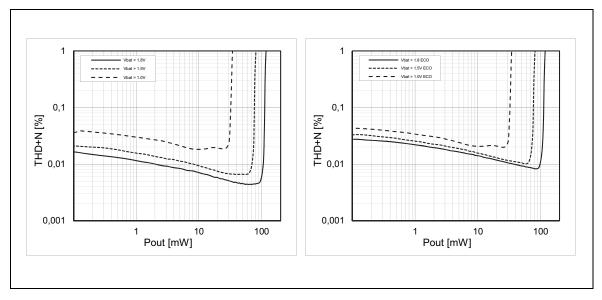

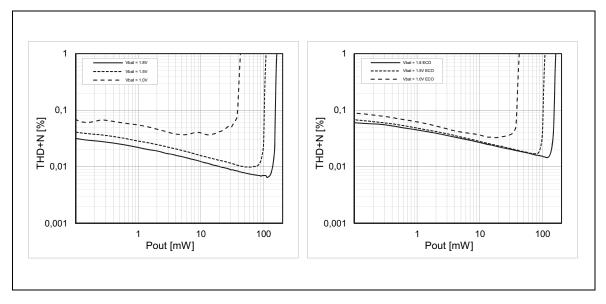

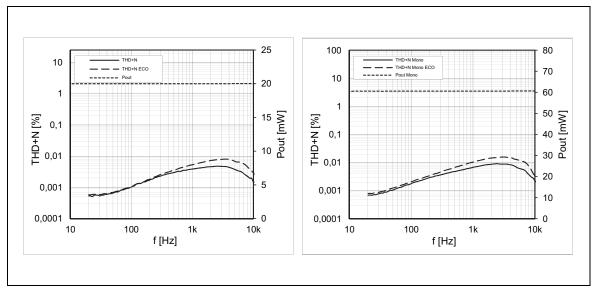

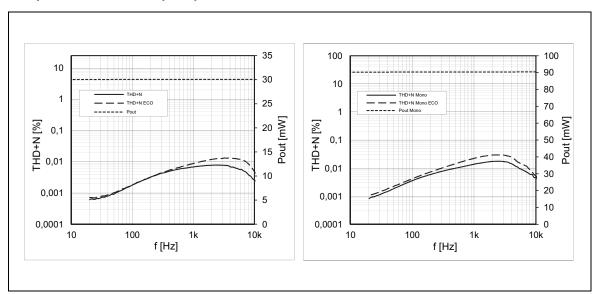

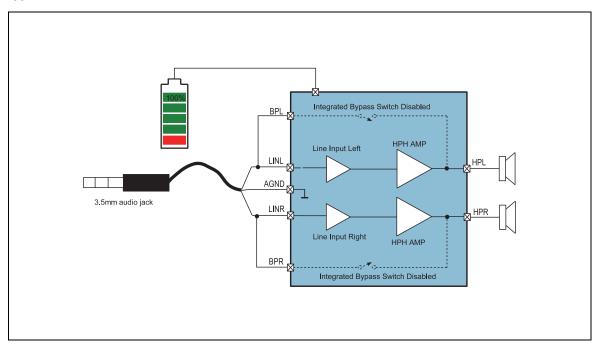

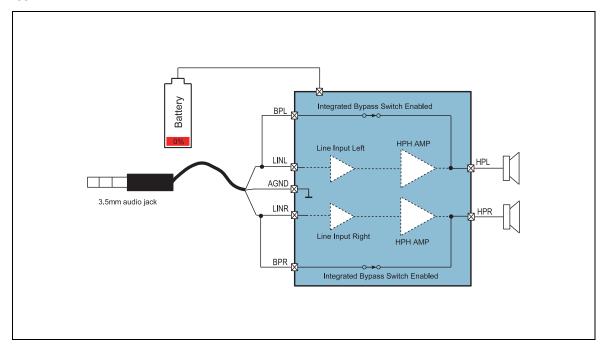

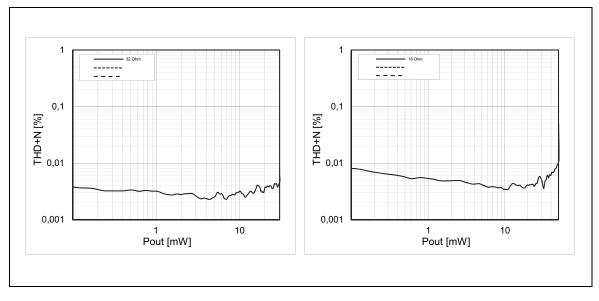

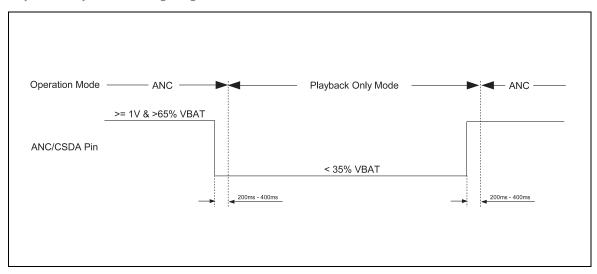

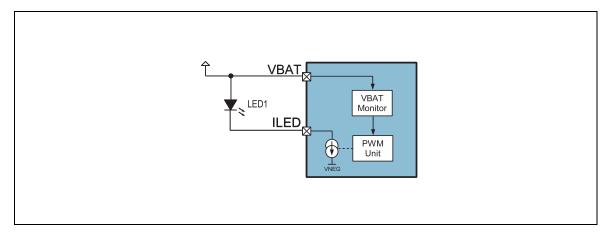

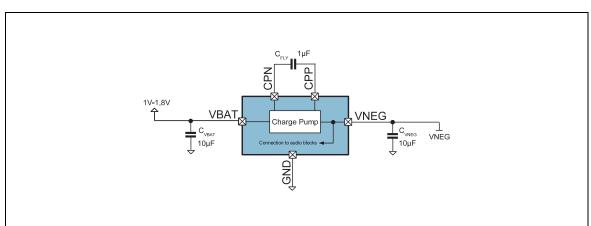

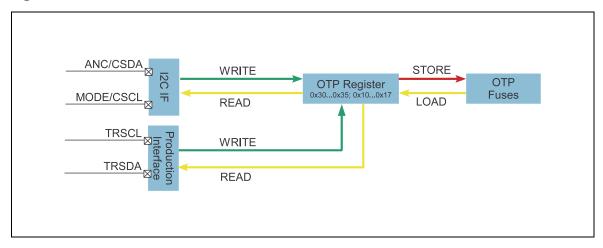

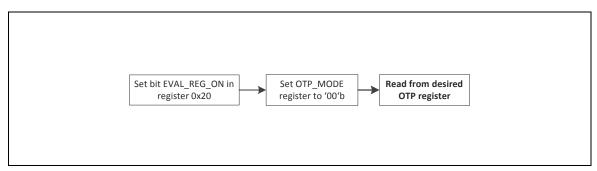

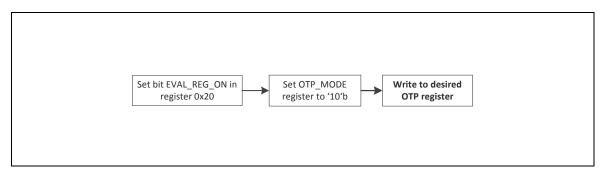

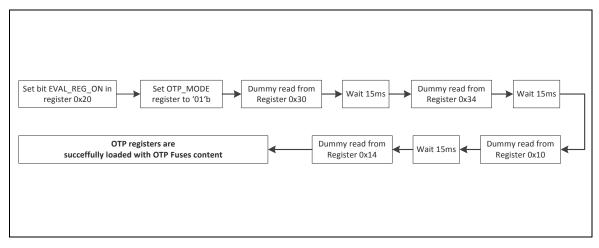

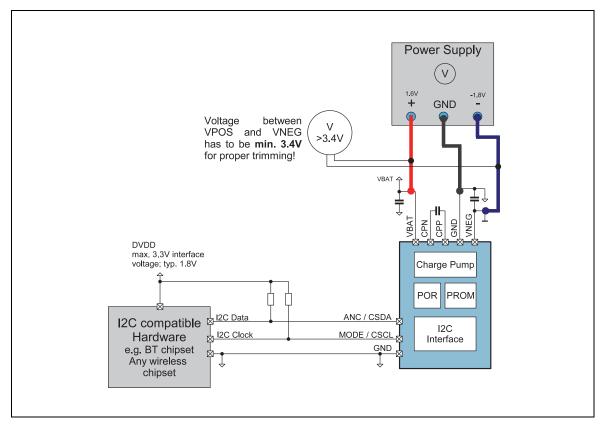

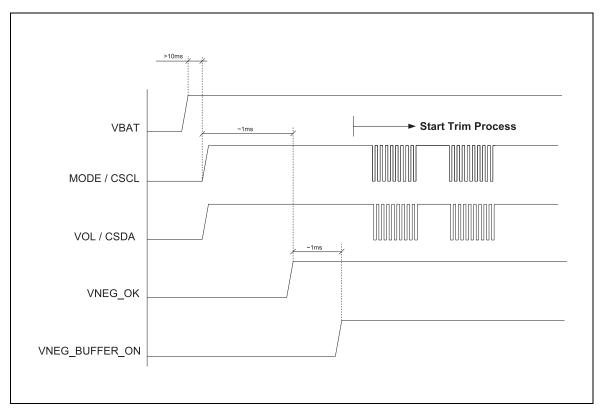

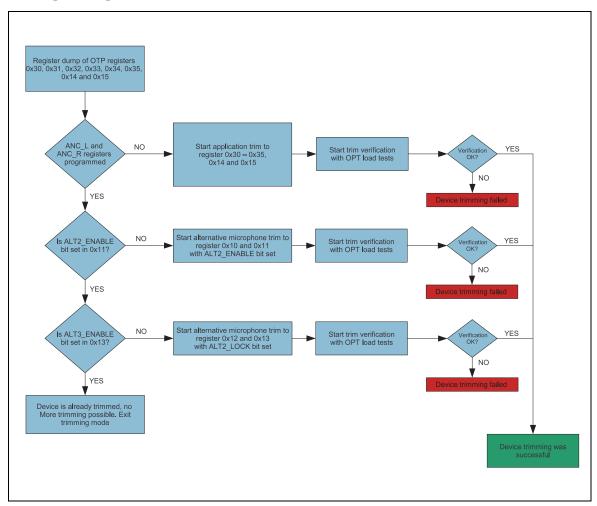

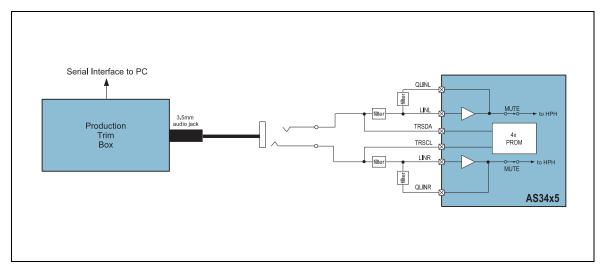

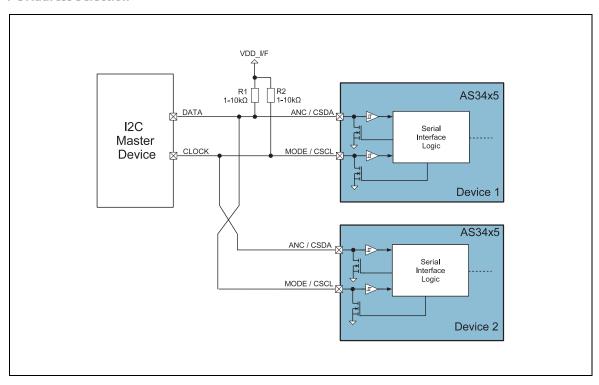

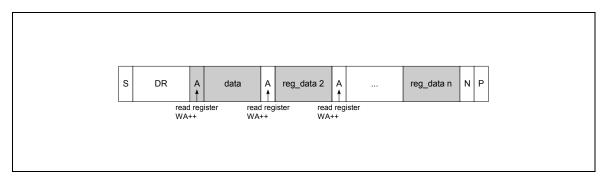

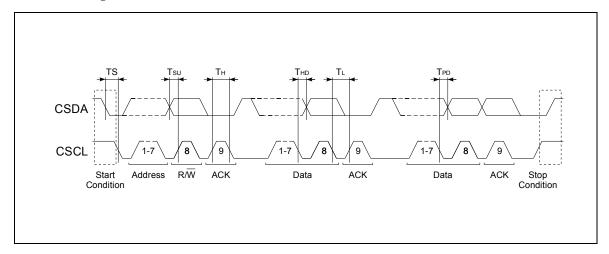

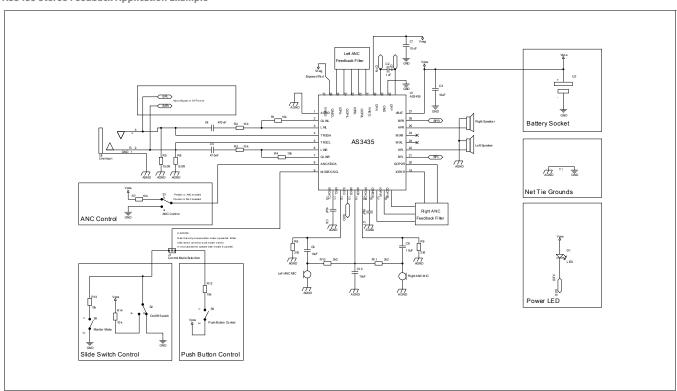

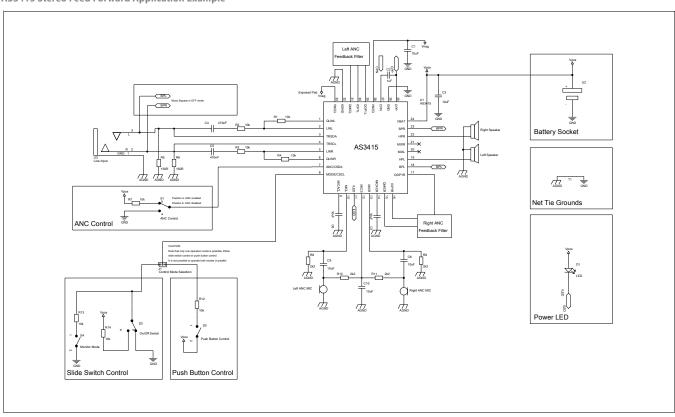

| $V_{TRIM}$ Application Trim Pins TRSCL and TRSDA $\begin{bmatrix} -0.3 \\ or \\ -1.8 \end{bmatrix}$ $\begin{bmatrix} -0.3 \\ or \\ -1.8 \end{bmatrix}$ $\begin{bmatrix} V_{BAT} \\ V_{BAT} \end{bmatrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>CP</sub>                                                                             | Charge Pump pins      | CPN, CPP                                                                | V <sub>NEG</sub> |     | V <sub>BAT</sub> | V    |   |  |