# Precision Integrated Analog Front End, Controller, and PWM for Battery Test and Formation Systems

Data Sheet AD8452

#### **FEATURES**

CC and CV battery test and formation modes with transparent and automatic switchover, for systems of 20 Ah or less

Precise measurement of voltage and current

Independent feedback control blocks

Highly accurate, factory trimmed instrumentation and

differential amplifiers

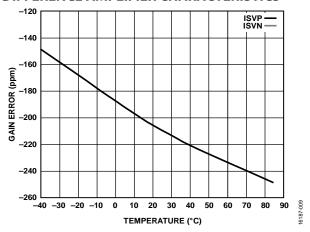

In-amp for current sense gain: 66 V/V Difference amplifier for voltage sense gain: 0.4 V/V Stable over temperature: offset voltage drift <0.6  $\mu$ V/°C (maximum)

Gain drift: <3 ppm/°C (maximum)

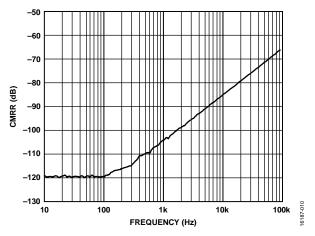

Current sense CMRR: 120 dB minimum

Popular SMPS control for charge/discharge

High PWM linearity with internal ramp voltage

50 kHz to 300 kHz user controlled switching frequency

Synchronization output or input with adjustable phase shift

Programmable soft start

#### **APPLICATIONS**

Battery formation and testing High efficiency battery test systems with recycle capability Battery conditioning (charging and discharging) systems

#### GENERAL DESCRIPTION

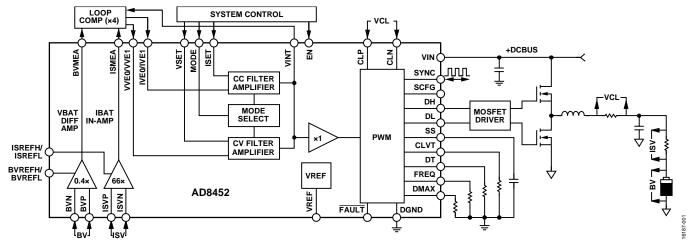

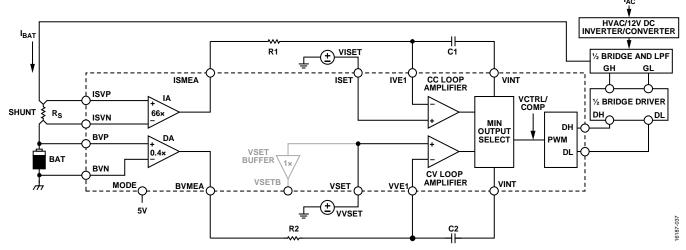

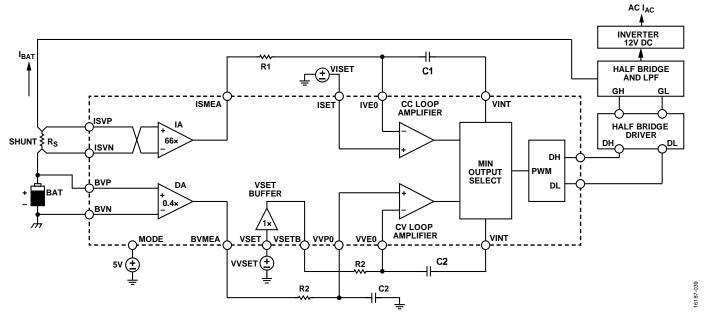

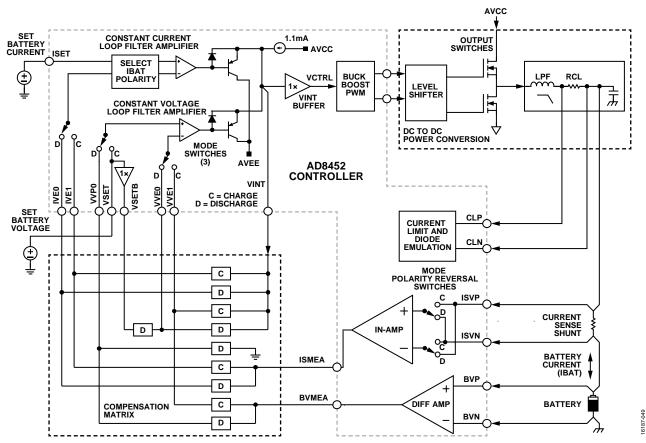

The AD8452 combines a precision analog front-end controller and switch mode power supply (SMPS), pulse-width modulator (PWM) driver into a single silicon platform for high volume battery testing and formation manufacturing. A precision instrumentation amplifier (in-amp) measures the battery charge/discharge current, while an equally accurate difference amplifier measures the battery voltage. Internal laser trimmed resistor networks establish the in-amp and difference amplifier gains (66 V/V and 0.4 V/V, respectively), and stabilize the AD8452 performance across the rated operating temperature range.

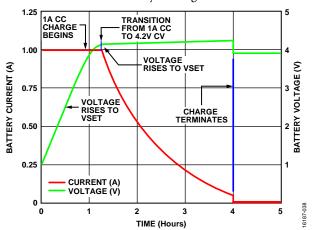

Desired battery cycling current and voltage levels are established by applying precise control voltages to the ISET and VSET inputs. Actual charge and discharge current levels are sensed (usually by a high power, highly accurate shunt resistor) whose value is carefully selected according to system parameters. Switching between constant current (CC) and constant voltage (CV) loop integration is instantaneous, automatic, and completely transparent to the observer. A logic high at the MODE input selects the charge or discharge mode (high for charge, low for discharge).

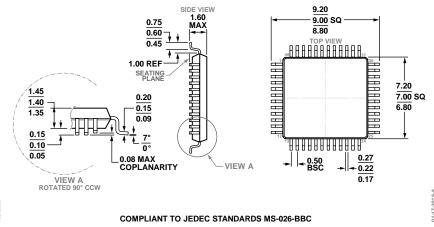

The AD8452 simplifies designs by providing excellent performance, functionality, and overall reliability in a space saving 48-lead, 7 mm  $\times$  7 mm  $\times$  1.4 mm LQFP package rated for operation at temperatures from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

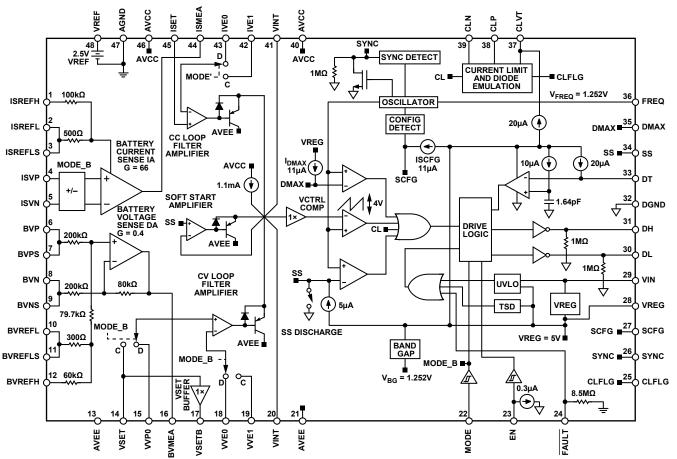

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## **TABLE OF CONTENTS**

| Features                                         | 1  |

|--------------------------------------------------|----|

| Applications                                     | 1  |

| General Description                              | 1  |

| Functional Block Diagram                         | 1  |

| Revision History                                 | 2  |

| Specifications                                   | 3  |

| Analog Front-End and Controller Specifications   | 3  |

| Pulse-Width Modulator Specifications             | 5  |

| Digital Interface Specifications                 | 6  |

| Power Supply                                     |    |

| Temperature Range Specifications                 | 7  |

| Absolute Maximum Ratings                         |    |

| Thermal Resistance                               | 8  |

| ESD Caution                                      | 8  |

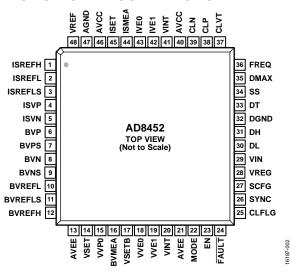

| Pin Configuration and Function Descriptions      | 9  |

| Typical Performance Characteristics              |    |

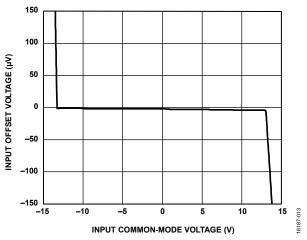

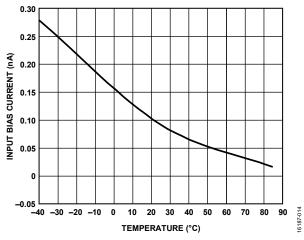

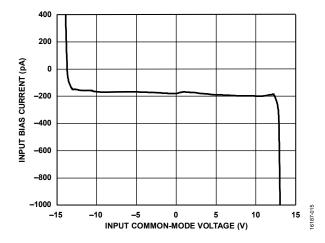

| In-Amp Characteristics                           |    |

| Difference Amplifier Characteristics             | 12 |

| CC and CV Loop Filter Amplifiers and VSET Buffer |    |

| where Noted)                                     |    |

| Reference Characteristics                        | 15 |

| Pulse-Width Modulator                            | 16 |

| Theory of Operation                              | 18 |

| Introduction                                     | 18 |

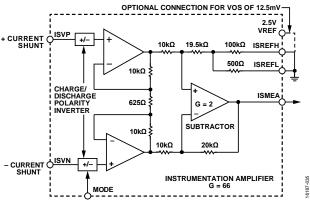

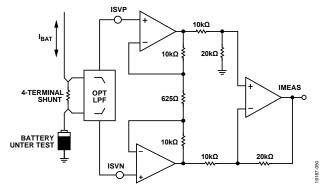

| Instrumentation Amplifier (In-Amp)               | 19 |

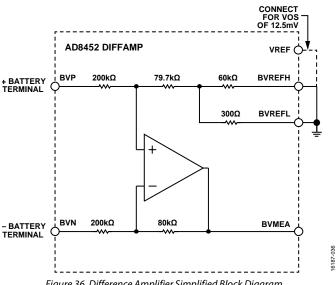

| Difference Amplifier                             | 20 |

| CC and CV Loop Filter Amplifiers                 |    |

| Charge and Discharge Control                     | 23 |

| Input and Output Supply Pins                     | 23 |

|                                                  |    |

| REVISION HISTORY                                 |    |

| 10/2018—Rev. 0 to Rev. A                         |    |

| Changes to Figure 34 and Figure 35               | 19 |

| Changes to Figure 38                             | 21 |

| Changes to Figure 47                             | 26 |

| Changes to Figure 49                             |    |

| Changes to Figure 50                             |    |

| Updated Outline Dimensions                       | 34 |

| Undervoltage Lockout (UVLO)                                            | 24 |

|------------------------------------------------------------------------|----|

| Soft Start                                                             | 24 |

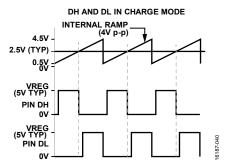

| PWM Drive Signals                                                      | 25 |

| Peak Current Protection and Diode Emulation (Synchronous)              | 25 |

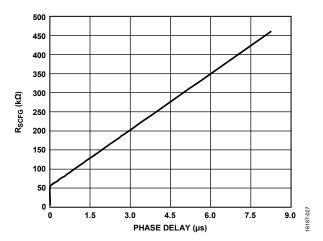

| Frequency and Phase Control                                            | 26 |

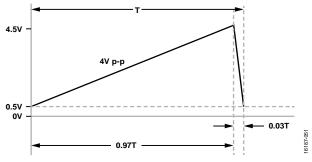

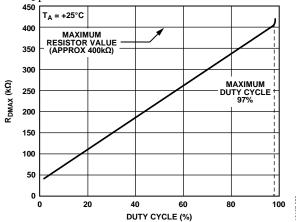

| Maximum Duty Cycle                                                     | 26 |

| Fault Input                                                            | 27 |

| Thermal Shutdown (TSD)                                                 | 27 |

| Applications Information                                               | 28 |

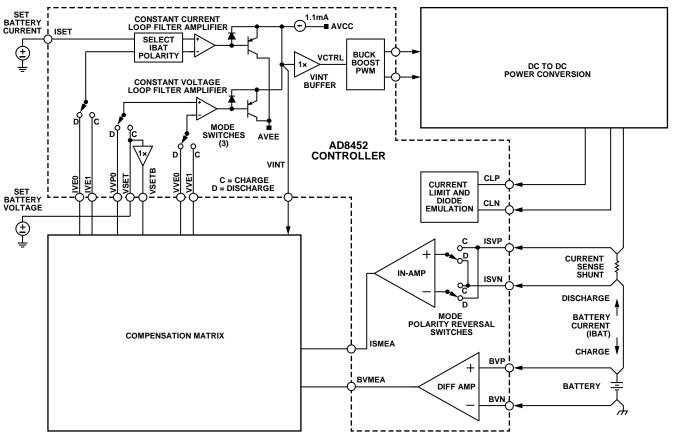

| Analog Controller                                                      | 28 |

| Functional Description                                                 | 28 |

| Power Supply Connections                                               | 29 |

| Current Sense In-Amp Connections                                       | 29 |

| Voltage Sense Differential Amplifier Connections                       | 29 |

| Battery Current and Voltage Control Inputs (ISET and VSET)             | 29 |

| Loop Filter Amplifiers                                                 | 30 |

| Selecting Charge or Discharge Options                                  | 30 |

| Select RCL and RCLVT for the Peak Current Limit                        | 30 |

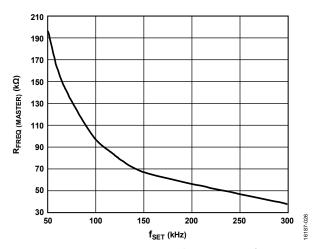

| Setting the Operating Frequency and Programming the Synchonization Pin | 31 |

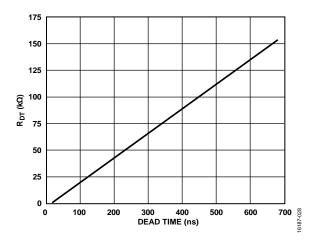

| Programming the Maximum Duty Cycle                                     | 32 |

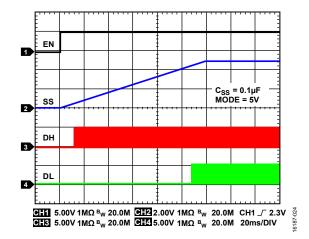

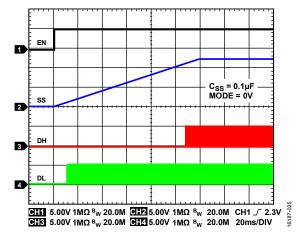

| Selecting C <sub>SS</sub>                                              | 33 |

| Additional Information                                                 | 33 |

| Outline Dimensions                                                     | 34 |

| Ordering Guide                                                         | 34 |

| 10/2018—Rev. 0 to Rev. A           |    |

|------------------------------------|----|

| Changes to Figure 34 and Figure 35 | 19 |

| Changes to Figure 38               | 2  |

| Changes to Figure 47               | 20 |

| Changes to Figure 49               | 28 |

| Changes to Figure 50               | 29 |

| Updated Outline Dimensions         | 34 |

| •                                  |    |

10/2017—Revision 0: Initial Version

## **SPECIFICATIONS**

AVCC = 15 V, AVEE = -15 V, VIN = 24 V, and  $T_A$  = 25°C, unless otherwise noted.

#### **ANALOG FRONT-END AND CONTROLLER SPECIFICATIONS**

Table 1.

| Parameter                               | Test Conditions/Comments                 | Min        | Тур  | Max        | Unit    |

|-----------------------------------------|------------------------------------------|------------|------|------------|---------|

| CURRENT SENSE INSTRUMENTATION AMPLIFIER |                                          |            |      |            |         |

| Gain                                    |                                          |            | 66   |            | V/V     |

| Gain Error                              | $V_{ISMEA} = \pm 10 \text{ V}$           |            |      | ±0.1       | %       |

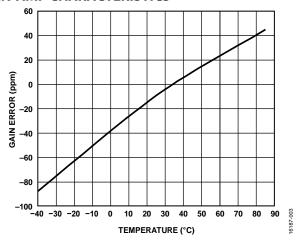

| Gain Drift                              | $T_A = T_{MIN}$ to $T_{MAX}$             |            |      | 3          | ppm/°C  |

| Offset Voltage Referred to Input (RTI)  | ISREFH pin and ISREFL pin grounded       | -100       |      | +100       | μV      |

| Offset Voltage Drift                    | $T_A = T_{MIN}$ to $T_{MAX}$             | -0.6       | -0.1 | +0.6       | μV/°C   |

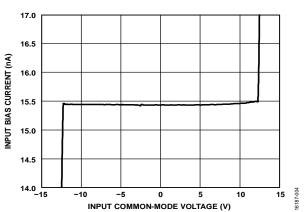

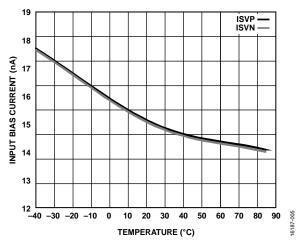

| Input Bias Current                      |                                          |            | 15   | 30         | nA      |

| Input Common-Mode Voltage Range         | $V_{ISVP} - V_{ISVN} = 0 V$              | AVEE + 2.3 |      | AVCC - 2.4 | V       |

| Differential Input Impedance            |                                          |            | 150  |            | GΩ      |

| Common-Mode Input Impedance             |                                          |            | 150  |            | GΩ      |

| Output Voltage Swing                    | $RL = 10 \text{ k}\Omega$                | AVEE + 1.5 |      | AVCC - 1.2 | V       |

| Reference Input Voltage Range           | ISREFH pin and ISREFL pin tied together  | AVEE + 1.5 |      | AVCC - 1.5 | V       |

| Reference Bias Current                  | $V_{ISVP} = V_{ISVN} = 0 V$              |            | 5    |            | μΑ      |

| Output Voltage Level Shift              | ISREFL pin grounded                      |            |      |            |         |

| Maximum                                 | ISREFH pin connected to VREF pin         | 11         | 12.5 | 14         | mV      |

| Scale Factor                            | V <sub>ISMEA</sub> /V <sub>ISREFH</sub>  | 4.4        | 5    | 5.6        | mV/V    |

| Short-Circuit Current                   |                                          |            | 40   |            | mA      |

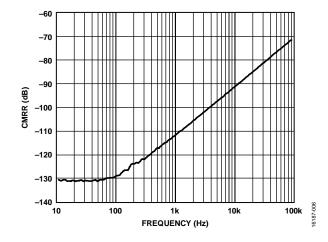

| Common-Mode Rejection Ratio (CMRR)      | $\Delta V_{CM} = 20 \text{ V}$           | 120        |      |            | dB      |

| Temperature Coefficient                 | $T_A = T_{MIN}$ to $T_{MAX}$             |            |      | 0.01       | μV/V/°C |

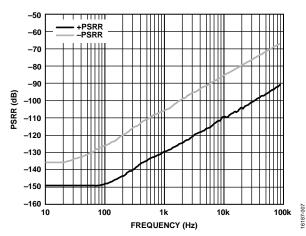

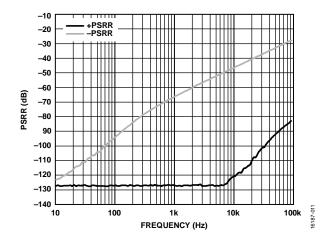

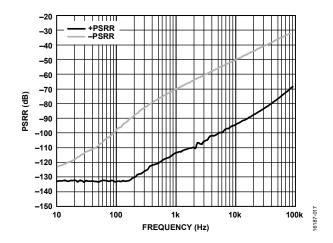

| Power Supply Rejection Ratio (PSRR)     | $\Delta V_S = 10 \text{ V}$              | 122        | 140  |            | dB      |

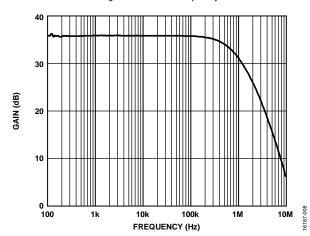

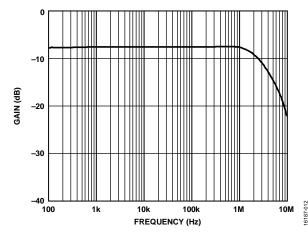

| Small Signal –3 dB Bandwidth            |                                          |            | 675  |            | kHz     |

| Slew Rate                               | $\Delta V_{ISMEA} = 10 \text{ V}$        |            | 5    |            | V/µs    |

| VOLTAGE SENSE DIFFERENCE AMPLIFIER      |                                          |            |      |            |         |

| Gain                                    |                                          |            | 0.4  |            | V/V     |

| Gain Error                              | $V_{IN} = \pm 10 \text{ V}$              |            |      | ±0.1       | %       |

| Gain Drift                              | $T_A = T_{MIN}$ to $T_{MAX}$             |            |      | 3          | ppm/°C  |

| Offset Voltage Referred to Output (RTO) | BVREFH pin and BVREFL pin grounded       | -250       |      | +250       | μV      |

| Offset Voltage Drift                    | $T_A = T_{MIN}$ to $T_{MAX}$             | -2         | -0.1 | +2         | μV/°C   |

| Differential Input Voltage Range        | $V_{BVN} = 0 V$ , $V_{BVREFL} = 0 V$     | -17        |      | +17        | V       |

| Input Common-Mode Voltage Range         | $V_{BVMEA} = 0 V$                        | -40        |      | +40        |         |

| Differential Input Impedance            |                                          |            | 400  |            | kΩ      |

| Input Common-Mode Impedance             |                                          |            | 140  |            | kΩ      |

| Output Voltage Swing                    | $RL = 10 \text{ k}\Omega$                | AVEE + 1.5 |      | AVCC - 1.2 | V       |

| Reference Input Voltage Range           | BVREFH pin and BVREFL pin connected      | AVEE + 1.5 |      | AVCC - 1.5 | V       |

| Output Voltage Level Shift              | BVREFL pin grounded                      |            |      |            |         |

| Maximum                                 | BVREFH pin connected to VREF pin         | 11.0       | 12.5 | 14.0       | mV      |

| Scale Factor                            | V <sub>BVMEA</sub> /V <sub>BVREFH</sub>  | 4.4        | 5    | 5.6        | mV/V    |

| Short-Circuit Current                   |                                          |            | 40   |            | mA      |

| CMRR                                    | $\Delta V_{CM} = 10 \text{ V, RTO}$      | 90         |      |            | dB      |

| Temperature Coefficient                 | $T_A = T_{MIN}$ to $T_{MAX}$             |            |      | 0.05       | μV/V/°C |

| PSRR                                    | $\Delta V_S = 10 \text{ V, RTO}$         | 114        | 123  |            | dB      |

| Small Signal –3 dB Bandwidth            |                                          |            | 3.0  |            | MHz     |

| Slew Rate                               | $\Delta V_{\text{BVMEA}} = 10 \text{ V}$ |            | 0.9  |            | V/µs    |

| Parameter                           | Test Conditions/Comments                       | Min        | Тур   | Max        | Unit   |

|-------------------------------------|------------------------------------------------|------------|-------|------------|--------|

| CC AND CV LOOP FILTER AMPLIFIERS    |                                                |            |       |            |        |

| Offset Voltage                      |                                                |            |       | 150        | μV     |

| Offset Voltage Drift                | $T_A = T_{MIN}$ to $T_{MAX}$                   | -1         | +0.02 | 1          | μV/°C  |

| Input Bias Current                  |                                                | -5         |       | +5         | nA     |

| Input Common-Mode Voltage Range     |                                                | AVEE + 1.5 |       | AVCC - 1.8 | V      |

| Output Voltage Swing                | V <sub>VINT</sub> voltage range                | AVEE + 1.5 |       | 5          | V      |

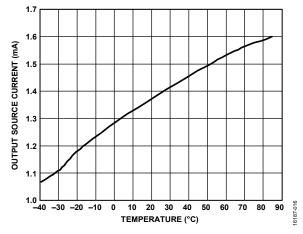

| Source Short-Circuit Current        |                                                |            | 1     |            | mA     |

| Sink Short-Circuit Current          |                                                |            | 40    |            | mA     |

| PSRR                                | $\Delta V_S = 10 \text{ V}$                    | 113        | 122   |            | dB     |

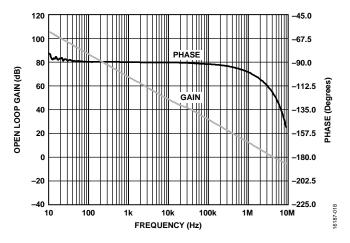

| Small Signal Gain Bandwidth Product |                                                |            | 3     |            | MHz    |

| Slew Rate                           | $\Delta V_{VINT} = 10 V$                       |            | 1     |            | V/µs   |

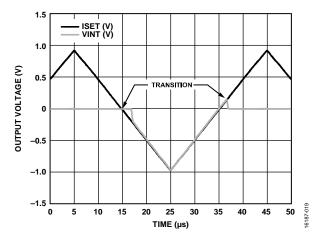

| CC to CV Transition Time            |                                                |            | 1.8   |            | μs     |

| VSET VOLTAGE BUFFER                 |                                                |            |       |            |        |

| Nominal Gain                        |                                                |            | 1     |            | V/V    |

| Offset Voltage                      |                                                |            |       | 150        | μV     |

| Offset Voltage Drift                | $T_A = T_{MIN}$ to $T_{MAX}$                   | -1         | +0.06 | +1         | μV/°C  |

| Input Bias Current                  |                                                | -5         |       | +5         | nA     |

| Input/Output Voltage Range          |                                                | AVEE + 1.5 |       | AVCC - 1.8 | V      |

| Short-Circuit Current               |                                                |            | 40    |            | mA     |

| PSRR                                | $\Delta V_S = 10 \text{ V}$                    | 113        | 122   |            | dB     |

| Small Signal –3 dB Bandwidth        |                                                |            | 4     |            | MHz    |

| Slew Rate                           | $\Delta V_{VSETBF} = 10 \text{ V}$             |            | 1     |            | V/µs   |

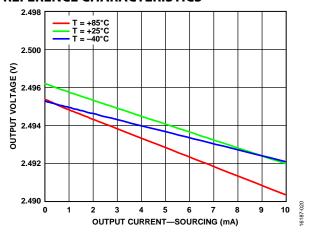

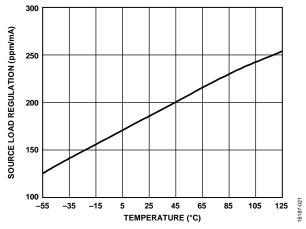

| VOLTAGE REFERENCE                   |                                                |            |       |            |        |

| Nominal Output Voltage              | With respect to AGND                           |            | 2.5   |            | V      |

| Output Voltage Error                |                                                |            |       | ±1         | %      |

| Temperature Drift                   | $T_A = T_{MIN}$ to $T_{MAX}$                   |            |       | 16         | ppm/°C |

| Line Regulation                     | $\Delta V_S = 10 \text{ V}$                    |            |       | 10         | ppm/V  |

| Load Regulation                     | $\Delta I_{VREF} = 1 \text{ mA (source only)}$ |            |       | 300        | ppm/m/ |

| Source Short-Circuit Current        |                                                |            | 15    |            | mA     |

### **PULSE-WIDTH MODULATOR SPECIFICATIONS**

Table 2.

| Parameter                                   | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min  | Тур   | Max  | Unit |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

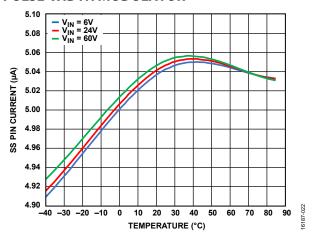

| SOFT START (SS)                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |       |      |      |

| SS Pin Current                              | $V_{SS} = 0 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4    | 5     | 6    | μΑ   |

| SS Threshold Rising                         | Switching enable threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 0.52  | 0.65 | V    |

| SS Threshold Falling                        | Switching disable threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.4  | 0.5   |      | V    |

| End of Soft Start                           | Asynchronous to synchronous threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.4  | 4.5   | 4.6  | V    |

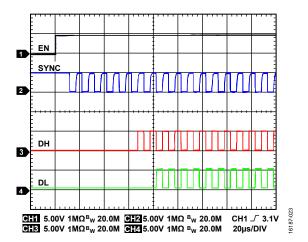

| PWM CONTROL                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |       |      |      |

| Frequency                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |       |      |      |

| Frequency Range                             | $R_{FREQ} = 33.2 \text{ k}\Omega \text{ to } 200 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50   |       | 300  | kHz  |

| Oscillator Frequency                        | $R_{FREQ} = 100 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 90   | 100   | 110  | kHz  |

| FREQ Pin Voltage                            | $R_{FREQ} = 100 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.1  | 1.255 | 1.4  | V    |

| SYNC Output (Internal Frequency<br>Control) | $V_{SCFG} \ge 4.53 \text{ V or SCFG pin floating}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |       |      |      |

| Internal SYNC Range                         | For SYNC output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50   |       | 300  | kHz  |

| SYNC Output Clock Duty Cycle                | $V_{SCFG} = V_{VREG}$ , $R_{FREQ} = 100 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40   | 50    | 60   | %    |

| SYNC Sink Pull Down Resistance              | $V_{SCFG} = 5 \text{ V, } I_{SYNC} = 10 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 10    | 20   | Ω    |

| SYNC Input (External Frequency Control)     | $V_{SCFG} < 4.25 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |       |      |      |

| External SYNC Range                         | For SYNC input clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50   |       | 300  | kHz  |

| SYNC Internal Pull-Down Resistor            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.5  | 1     | 1.5  | МΩ   |

| Maximum SYNC Pin Voltage                    | For external sync operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 5     |      | V    |

| SYNC Threshold Rising                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 1.2   | 1.5  | V    |

| SYNC Threshold Falling                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.7  | 1.05  |      | V    |

| SCFG                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |       |      |      |

| SCFG High Threshold                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |       |      |      |

| Rising                                      | SYNC set to input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | 4.53  | 4.7  | V    |

| Falling                                     | SYNC set to output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.25 | 4.47  |      | V    |

| SCFG Low Threshold                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |       |      |      |

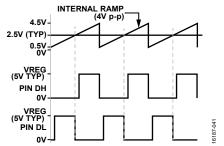

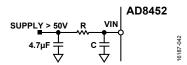

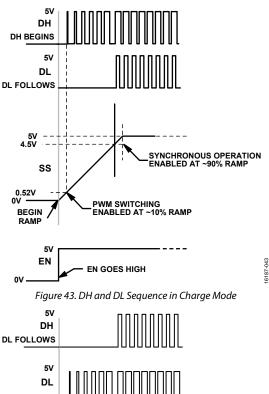

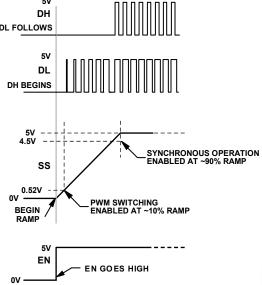

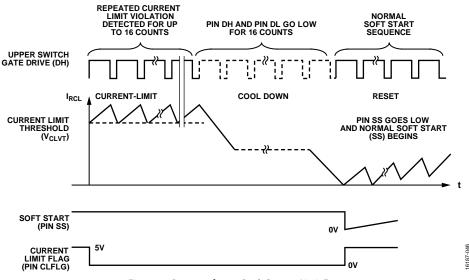

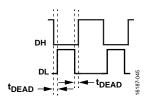

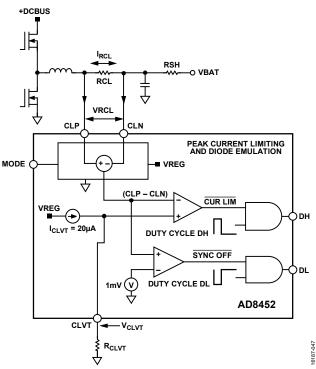

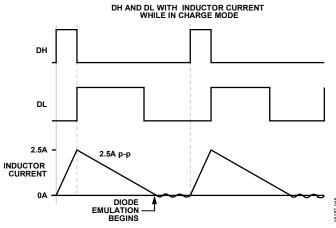

| Rising                                      | Programmable phase shift above threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 0.55  | 0.65 | V    |