Altera Cyclone® II FPGA

Altera Cyclone® II 90nm FPGA 的设计初衷在于实现低功耗,并向大批量、成本敏感型应用提供用户定制的多种功能。Cyclone II FPGA 可以与 ASIC 相媲美的成本提供更好的性能和更低的功耗。Cyclone II FPGA 将低成本 FPGA 的密度范围扩展至68,416个逻辑单元(LE),共有622个可用I/O引脚,并配有1.1Mbit嵌入式存储器。为确保快速可用性和降低成本,Cyclone II FPGA 采用了300mm晶圆和 TSMC 的90nm低k介电质工艺。通过减小硅片面积,Cyclone II 器件可以与 ASIC 相媲美的成本在单一芯片上实现复杂的数字系统。与竞争对手的 90nm FPGA 相比,Altera Cyclone II FPGA 性能高出了60%,功耗降低了一半。Cyclone II FPGA 具有成本最低和性能经过优化等特性,特别适用于汽车、消费电子、通信、视频处理、测试和测量以及其他终端市场解决方案等各种应用场合。特性

- High-density architecture with 4,608 to 68,416 LEs:

- M4K embedded memory blocks

- Up to 1.1Mbits of RAM available without reducing available logic

- 4,096 memory bits per block (4,608 bits per block including 512 parity bits)

- Variable port configurations of ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32, and ×36

- Embedded multipliers:

- Up to 150 18- × 18-bit multipliers are each configurable as two independent 9- × 9-bit multipliers with up to 250MHz performance

- Optional input and output registers

- Flexible clock management circuitry:

- Hierarchical clock network for up to 402.5MHz performance

- Up to four PLLs per device provide clock multiplication and division, phase shifting, programmable duty cycle, and external clock outputs, allowing system-level clock management and skew control

应用

- Automotive

- Consumer

- Communications

- Video processing

- Test and measurement

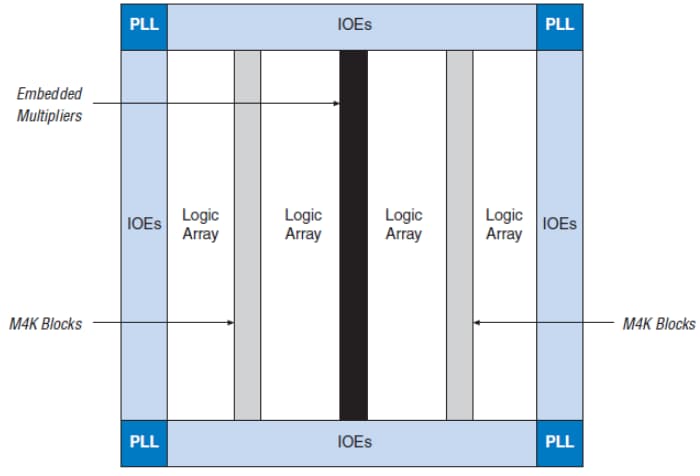

EP2C20 Block Diagram

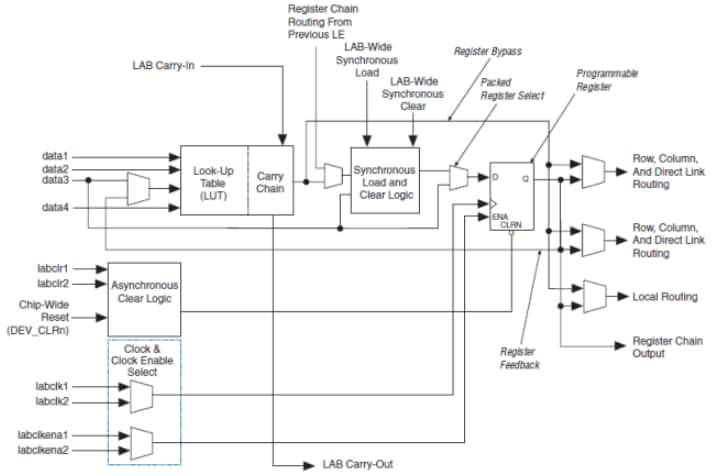

Cyclone 2 LE Figure

Additional Resource

View Results ( 4 ) Page

| 物料编号 | 数据表 | 逻辑元件数量 | 逻辑数组块数量——LAB | 输入/输出端数量 | 工作电源电压 | 最大工作频率 | 总内存 | 封装 / 箱体 |

|---|---|---|---|---|---|---|---|---|

| EP2C70F896C8N |  |

68416 LE | 4276 LAB | 622 I/O | 1.15 V to 1.25 V | 260 MHz | 1152000 bit | FBGA-896 |

| EP2C35F484C8 |  |

33216 LE | 2076 LAB | 322 I/O | 1.15 V to 1.25 V | 260 MHz | 483840 bit | FBGA-484 |

| EP2C70F672C8N |  |

68416 LE | 4276 LAB | 422 I/O | 1.15 V to 1.25 V | 260 MHz | 1152000 bit | FBGA-672 |

| EP2C70F672C7N |  |

68416 LE | 4276 LAB | 422 I/O | 1.15 V to 1.25 V | 260 MHz | 1152000 bit | FBGA-672 |

发布日期: 2012-11-16

| 更新日期: 2026-01-07