BittWare XUP-P3R FPGA加速器卡

BittWare XUP-P3R FPGA加速器卡是一款基于Xilinx Virtex UltraScale+ FPGA的3/4长度PCIe x16卡,可为需要大规模数据流和数据包处理的系统提供高性能、高带宽和更低延迟。XUP-P3R卡提供各种内存配置,包括支持高达512GB的内存、精密的时钟和计时选项以及四个前面板QSFP壳体,每个壳体均支持100Gbps (4x25) 和100GbE。串行扩展端口 (SEP) 可让XUPP3R扩展为额外的PCIe Gen3 x16插槽,对4个QSFP,或者两个XUPP3R之间的连接起到补充作用。BittWare XUP-P3R FPGA加速器卡集成了板管理控制器 (BMC),用于高级系统监控以及简化平台集成和管理。XUP-P3R非常适合数据中心应用,包括网络处理和安全、加速、存储、广播和信号情报。特性

- 各种内存配置,高达512GB DDR4

- 集成BMC,用于高级系统监控

- 4个100GbE(通过4个QSFP28)

- Xilinx 2.500万LC FPGA,高达VU9P

- 简化平台集成和管理

规范

- FPGA

- Virtex UltraScale+ VU9P

- 内核速度等级 – 2

- 板载闪存,用于启动FPGA

- 外部存储器

- 4个DIMM插槽,每个均支持

- 高达128GB DDR4 x72,带ECC

- 高达576Mb双QDR-II+ x18(2个独立288Mb组)

- 4个DIMM插槽,每个均支持

- 16个Gen3主机接口直接连接FPGA

- Micro USB 2.0端口,用于FPGA和闪存调试和编程

- 串行扩展端口 (SEP)

- 通过20x GTY收发器扩展接口到FPGA(可选;需要第二个插槽)

- 14个至FPGA的GPIO信号

- 电路板管理控制器

- 电压、电流和温度监控

- 电源排序和复位

- 现场升级

- FPGA配置和控制

- 时钟配置

- I2C总线访问

- USB 2.0

- 电压覆盖

- 电压、电流和温度监控

- FPGA开发

- QSFP壳体

- 前面板上的4个QSFP28 (zQSFP) 壳体,通过16个收发器直接连接到FPGA

- 每个均支持100GbE、40GbE、4个25GbE或4个10GbE,并可组合为400GbE

- 散热

- 双宽度有源风扇和散热片 - 标配

- 双宽度无源散热片 - 可选

- 双宽度高级无源冷却(带散热管)- 可选

- 电气规格

- 板载电源,源自12V PCIe插槽和AUX连接器(6引脚)

- 功率耗散取决于应用

- 工作温度范围:+5°C至+35°C

- 外观尺寸

- 3/4长度、标准高度PCIe双插槽板

- 9.4英寸x4.37英寸

- 应用开发

- HDL/Verilog

- BittWorks II工具包 - 用于BittWare硬件的主机、命令和调试工具

- Xilinx Vivado设计套件

- OpenCL - Xilinx SDAccel开发环境、SDAccel平台版本和预先构建的XUP-P3R示例

- HDL/Verilog

Compliances

• FCC (USA) 47CFR15.107 / 47CFR15.109

• CE (Europe) EN 55032:2015/A11:2020 / EN55024:2010 / EN 55035:2017 / EN 61000-3-2:2014 / EN 610003-3:2013

• UKCA (United Kingdom) BS EN 55032:2012/AC:2013 / BS EN55024:2010 / BS EN 55035:2017 / BS EN 61000-3-2:2014 / BS EN 610003-3:2013

• ICES (Canada) ICES-003 issue 7

• Safety objectives referred to in Article 3 and set out in Annex I of DIRECTIVE 2014/35/EU have been fulfilled

• RoHS compliant to the 2011/65/EU + 2015/863 directive

视频

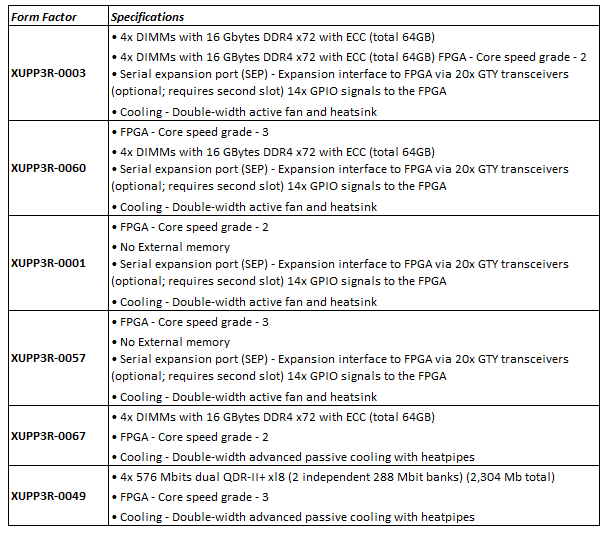

外形尺寸比较表

散热选项

SEP模块示意图

框图

信息图

发布日期: 2020-06-11

| 更新日期: 2025-10-15