通过Lattice Radiant™软件提高设计效率,该软件支持大型复杂设计,具有业界领先的RTL合成、统一的设计数据库、高级脚本、现代GUI、定时分析和嵌入式逻辑分析仪。Lattice还为MachXO4™系列提供了广泛的预设IP模块。

特性

- 型号(所有型号在功能和引脚上均兼容)

- ZC - 超低功耗,2.5V/3.3V电源

- HC - 高性能,2.5V/3.3V电源

- HE - 高性能,1.2V电源

- 基于65nm的非易失性低功耗工艺

- 极低功耗,静态功耗低至140µW

- 广泛的896 LUT至9400 LUT逻辑密度选择范围

- 内嵌闪存,用户闪存(UFM)最多可达448kb

- 内嵌块存储器(EBR)最多可达432kb,分布式RAM为54kb

- 开机即用,启动时间不到5ms

- 高度灵活的缓冲器支持3.3V、1V I/O标准,用于连接旧版和新一代设备

- 支持热插拔,漏电流低至350µA,无电源排序

- 支持LVCMOS和LVTTL I/O类型的混合电压

- 默认集成上拉电阻器,以减少外部组件

- I/O引脚与LUT比率高的紧凑型封装,多达382个I/O引脚

- SPI、I2C、定时器/计数器和振荡器等片上硬化功能

- 使用Lattice Radiant软件提高设计生产力

- 符合RoHS标准

应用

- 计算

- 数据中心服务器

- 网络和存储器

- 硬件加速

- 通信

- 以太网开关和路由器

- 宽带接入

- 无线电单元

- 消费类电子产品

- 显示器

- 摄像头

- 智能手机

- 工业

- 电机控制

- 手持设备

- 测试与测量

- 可编程逻辑控制器

- 汽车(零件尾号为A)

- ADAS

- 逆变器

- 电机控制

- 信息娱乐

- 电池管理

规范

- 低功耗和可编程架构

- 逻辑密度范围为896至9.4k LUT4

- 64kb至432kb的嵌入式块存储器(EBR)

- 高达54kb的分布式RAM

- 专用FIFO控制逻辑

- 先进的65nm低功耗工艺

- 可编程低摆幅差分I/O

- 待机模式和其他节能选项

- 高性能、灵活的I/O缓冲器

- 可编程sysI/O™缓冲器支持广泛的接口范围

- LVCMOS 3.3/2.5/1.8/1.5/1.2/1.0

- LVTTL

- LVDS、Bus-LVDS、MLVDS、LVPECL

- 模拟MIPI D-PHY

- 施密特触发输入,迟滞最高为0.5V

- I/O支持热插座

- 片上差分终端

- 可编程上拉或下拉模式

- 可编程sysI/O™缓冲器支持广泛的接口范围

- 预先设计的源同步I/O:

- I/O单元中的DDR寄存器

- 专用传动逻辑

- 显示器I/O的7:1传动比

- 通用DDR、DDRx2和DDRx4

- 先进封装范围广泛

- I/O与LUT比率高达382个I/O引脚的紧凑型封装

- 0.4mm间距 - 1280至4320个LUT,占位面积极小的WLCSP(2.5mm×2.5mm至3.8mm×3.8mm),I/O为27至62个

- 0.5mm间距 - 8mmx8mm BGA至20mmx20mm TQFP封装中896至4320个LUT,I/O最多为112个

- 0.8mm间距 - 14mmx14mm至19mmx19mm BGA封装中1280至9400个LUT,I/O最多为382个

- 1.0mm间距 - 1280至4320 LUT,采用17mmx17mm BGA封装,有204个I/O

- 非易失性,可多次重新配置

- 即时开机 - 几毫秒内即可启动

- 可选双启动,带外部SPI存储器

- 单芯片安全解决方案

- 可通过JTAG、SPI或I2C实现可编程

- 可配置闪存,商业/工业设备可进行高达100,000次写/擦,汽车设备可进行10,000次写/擦

- 支持非易失性存储器的后台编程

- 通过TransFR重新配置,在I/O保持系统状态的同时进行现场逻辑更新

- 可优化片上时钟功能

- 商用/工业设备上的振荡器精度为5.5%

- 8个主时钟

- 最多支持两个边缘时钟,用于高速I/O接口,仅限顶部和底部。

- 每个器件最多可集成两个模拟 锁相环,并支持分数n频率合成。

- 输入频率范围宽广,从7MHz到400MHz

- 增强型系统级支持

- 片上硬化功能 - SPI、I2C和定时器/计数器

- 独特的TraceID用于系统跟踪

- 单电源,工作范围更广

- IEEE 1149.1标准边界扫描

- IEEE 1532合规系统内编程

- 最先进的设计软件

- Lattice Radiant支持MachXO4器件

- 行业领先的RTL语言支持VHDL、VHDL-2008、Verilog和SystemVerilog

- 命令行和TCL设计流程的高级脚本能力

- 一键编译流程和分析工具之间的交叉探测

- 嵌入式定时和逻辑分析仪

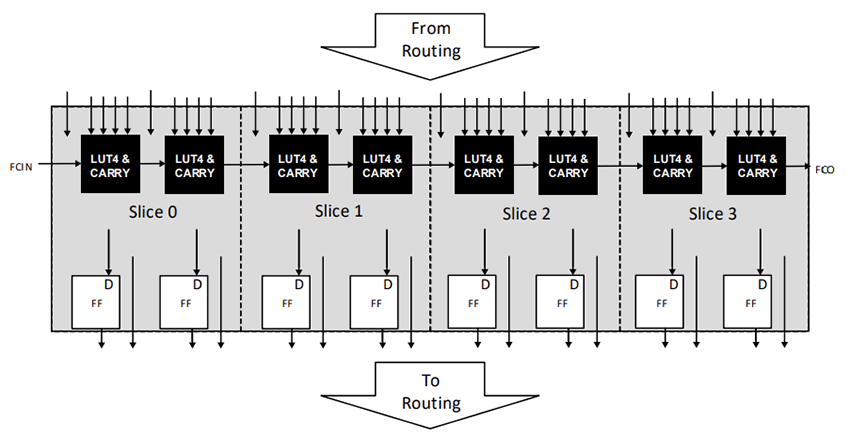

PFU框图

MachXO4器件的芯体由PFU块组成,这些PFU块可编程来执行逻辑、算术、分布式RAM和分布式ROM功能。每个PFU模块由四个互连的切片组成,编号为零至三。每个切片包含两个LUT和两个寄存器。每个PFU模块有53个输入和25个输出。

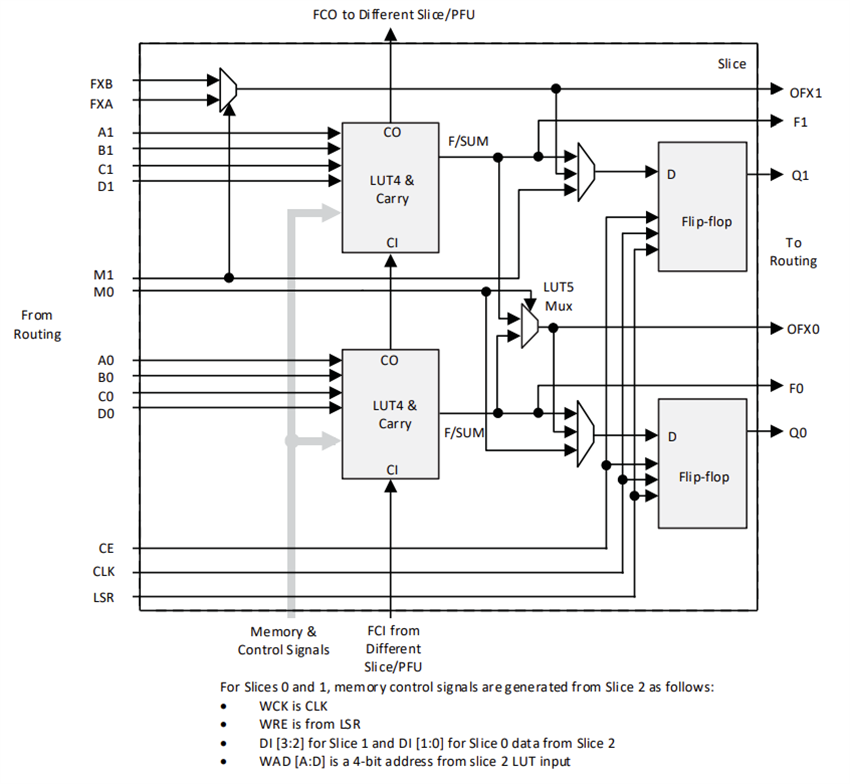

切片图

第0至3切片包含两个LUT4,为两个寄存器供电。第0至2切片可以配置为分布式存储器。控制逻辑执行设置/重置功能(可编程为同步/异步)、时钟选择、芯片选择以及更广泛的RAM/ROM功能。该切片中的寄存器可以配置为正/负时钟和边缘触发或电平敏感时钟。所有切片均有来自路由的15个输入和来自进位链的一个输入(来自相邻切片或PFU)。有七个输出:六个用于路由,一个用于进位链(用于相邻的PFU)。

PLL图

MachXO4 PLL包含一个WISHBONE端口功能,允许用户逻辑动态更改PLL设置(包括分频器值)。使用此功能时,必须在设计中实例化EFB块,以便访问WISHBONE端口。与动态相位调整类似,当通过WISHBONE端口更新PLL设置时,PLL可能会失去锁定,并且在tLOCK参数得到满足之前不会重新锁定。

发布日期: 2025-12-11

| 更新日期: 2025-12-22