|

|

|

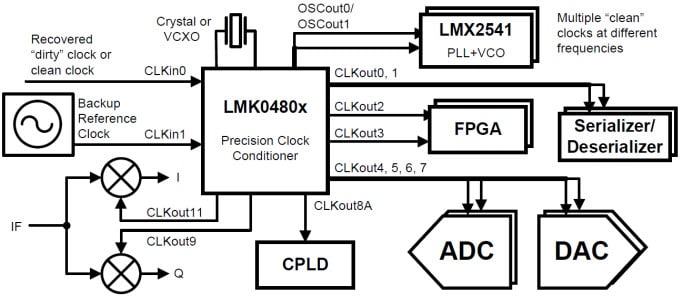

Texas Instruments LMK0480x 低噪声时钟抖动清除器

|

|

Texas Instruments LMK0480x 低噪声时钟抖动清除器是业界性能最佳的时钟调节器。它包括卓越的时钟抖动清除、生成和分配,配有先进的功能,可满足下一代系统的要求。双回路 PLLatinum™ 架构允许使用低噪声 VCXO 模块得到 111fs rms 的抖动(12kHz 至 20MHz)或使用低成本的外部晶体和变容二极管得到子 200fs rms 的抖动(12kHz 至 20MHz)。双环路架构包括两个高性能锁相环(PLL)、一个低噪晶体振荡器电路和一个高性能压控型振荡器(VCO)。第1 个 PLL (PLL1) 提供低噪声抖动清除器功能。而第 2 个 PLL (PLL2) 则执行时钟生成功能。

特性

- 超低 RMS 抖动性能

- 111fs RMS 抖动(12kHz至20MHz)

- 123fs RMS抖动(100Hz至20MHz)

- 双环路 PLLatinum™ PLL 架构

- PLL1

- 集成式低噪晶体振荡器电路

- 输入时钟丢失时保持模式

- 自动或手动触发/恢复

- PLL2

- 标准化锁相环 (PLL) 噪底为 –227dBc/Hz

- 相位检测器速率最高 155MHz

- OSCin 倍频器

- 集成式低噪 VCO

- 2个冗余输入时钟,带LOS

- 50% 的占空比输出除数,1至1045(偶数和奇数)

- 12 LVPECL、LVDS 或 LVCMOS 可编程输出

- 数字延迟,固定或动态可调

- 25ps 步进模拟延迟控制

- 14 差分输出,最多26 个单端

- 时钟速率达 1536MHz

- 0 延迟模式

|

- 通电时默认的三种时钟输出

- 多模:双 PLL、单 PLL 和时钟分配

- 工业温度范围:-40至85°C

- 3.15V 至 3.45V 工作电压

- 2 个专用缓冲/分频 OSCin 时钟

- 封装:64 引脚 WQFN (9.0 × 9.0 × 0.8 mm)

应用

- 数据转换计时

- 无线基础设施

- 组网、SONET/SDH、DSLAM

- 医疗/视频/军用/航空

- 测试与测量

|

|

|

简化示意图

|

LMK048xx 评估板

Texas Instruments LMK048xx 评估板简化了对带双回路 PLL 的 LMK048xxB 低噪声时钟抖动清除器的评估程序。TI CodeLoader 软件可用于通过 USB2ANY-uWire 接口对这些设备的内部寄存器进行编程。该评估板支持 LMK04800 系列中提供的任意四个设备。所有评估板均采用相同 PCB 布局和材料单,附着在板上的设备除外。商用品质的 VCXO 也安装到该板上,以提供一个已知参照点,用于评估该设备的性能和功能。

特性

- 多模:双 PLL、单 PLL 和时钟分配

- 双环路 PLLatinum™ PLL 架构

- 2个冗余输入时钟,带LOS

- 50%的占空比输出除数,1至1045(偶数和奇数)

- LVPECL、LVDS 或 LVCMOS 可编程输出

- 精确度数字延迟,固定或动态可调

- 25ps 步进模拟延迟控制

- 14 个差分输出,最多 26 个单端

- 0 延迟模式

|

|

|

DAC34SH84EVM评估模块(EVM)

Texas Instruments DAC34SH84EVM 评估模块(EVM)是一款可以让设计人员对TI的四通道、超低功耗、16 位、1.5 GSPS DAC34SH84 数模转换器(DAC)(带有32位宽 DDR LVDS 数据输入,集成 2x/4x/8x/16x 倍插值滤波器、32 位 NCO 和 PLL 以及在高 IF 下具有出色的线性功能)的性能进行评估的线路板。该评估模块为在各种时钟和数据输入以及 IF 输出条件下测试 DAC34SH84 提供灵活的环境。为便于使用,作为完整的IF发射器解决方案,DAC34SH84EVM包括CDCE62005时钟生成器/抖动清除器,用于为DAC34SH84计时。除了为DAC34SH84提供优质低抖动DAC采样时钟外,CDCE62005还为 TSW1400EVM(或TSW3100EVM)提供FPGA时钟作为FPGA参考时钟。

特性

- DAC34SH84 的综合测试能力

- 直接连接到 TSW1400/TSW3100 信号发生器

- 包含 CDCE62005,用于时钟发生或抖动清除

- 具有完整功能 GUI 的软件支持,以确保轻松测试和原型设计

- FMC-DAC-Adapter 卡兼容连接 Xilinx FPGA EVM 上提供的 FMC 互连接头

- 直接兼容 Altera FPGA EVM 上的 HSMC 接头

注:TSW1400EVM 支持高达 1.5GSPS LVDS 的切换速率,而 TSW3100EVM 只支持最高 1.25GSPS LVDS 切换速率。要充分评估每个数模转换器 DAC34SH84 的 750MSPS 数据速率,TSW1400EVM 必不可少。

|

|

|

TSW1265/TSW1266EVM Wideband 宽带双接收器参考设计

Texas Instruments TSW1265/TSW1266EVM 宽带双接收器参考设计是一个评估平台,非常适合用作发射器数字预失真的反馈接收器。每个评估模块信号链中都含有一个复杂的解调器 (LMH6521) 和 ADS5402 12 位模数转换器。通过修改板载滤波器元件,可以将信号链配置用于各种频率计划。两个评估板都包括 LMK04800 双 PLL 时钟抖动清除器和发生器,以提供板载低噪声计时解决方案。提供了软件 GUI,以便配置 ADS4249 和 LMK04800。可通过 GUI 或带 FPGA 的高速连接器来控制 LMH6521 DVGA 的增益。该评估模块设计用于与 TSW1400EVM 模式采集和生成板配合使用,以便从 ADS4249 中采集数据。然后可以通过高速数据转换器 Pro 软件工具执行信号分析。

特性

- 完整的射频至比特接收器评估平台利用双通道降低转换器、LMH6521 DVGA 和 ADS4249 14 位 250-MSPS ADC。

- LMK04800 时钟发生器和抖动清除提供了一个完整的板载时钟解决方案

- 提供了软件 GUI,以便配置 ADS4249、 LMK04800 和 LMH6521

- 易于与 TSW1400 模式采集和生成卡连接,进行快速评估

|

|

|

TSW3084EVM 评估模块

Texas Instruments TSW3084EVM 评估模块为电路板,可允许系统设计人员借助 LMK04806B 低噪声时钟发生器/抖动消除器,评估 TI 发射信号链的总性能。作为易于使用的完整射频发射解决方案,TSW3084EVM 包含用于为 DAC3484 数模转换器 (DAC) 提供计时的 LMK04806B,以及两个可将来自 4 通道 DAC 的 I/Q 输出上变频为射频载波的 TRF3705。DAC3484 是四通道超低功耗 16 位 1.25 GSPS DAC,带有有效的多路复用的 16 位宽总线,可实现每个 DAC 输入速率为 312MSPS。TRF3705 是高性能复数射频调制器,输出范围为 300MHz 至 4GHz。LMK04806B 是低噪声时钟发生器和抖动消除器,适用于低于 150fs rms 抖动量和高达 1300MHz 的输出频率。评估模块可以与 TSW3100/TSW1400 图形发生器结合使用,用于对 LVDS 端口执行大量测试步骤,直到达到 1.25 GSPS 的最大速率。TSW1406 可用于低成本、但速率高达 1 GSPS 的简单图形。除了向 DAC3484 提供高品质、低抖动的 DAC 采样时钟,LMK04806B 还向 TSW1400/TSW1406/TSW3100 提供作为 FPGA 参考时钟的 FPGA 时钟。发射射频信号路径还包括放大器和可编程衰减器。

|

|

特性

- 包含用于时钟生成和抖动消除的 LMK04806B

- 直接连接至 TSW3100/TSW1400/TSW1406 信号发生器

- 发送器(DAC3484 四路 DAC 和两个 TRF3705 IQ 调制器)对模拟基带、IF 和 RF 输出具有综合测试能力

- 具有完整功能 GUI 的软件支持,以确保轻松测试和原型设计

- FMC-DAC-Adapter 卡兼容连接 Xilinx FPGA EVM 上提供的 FMC 互连接头

- 直接兼容 Altera FPGA EVM 上的 HSMC 接头

|

|

TSW30H84EVM 评估模块

Texas Instruments TSW30H84EVM 评估模块为电路板,可允许系统设计人员借助 LMK04806B 低噪声时钟发生器/抖动消除器,评估 TI 发射信号链的总性能。作为易于使用的完整射频发射解决方案,TSW30H84EVM 包含用于为 DAC3484 数模转换器 (DAC) 提供计时的 LMK04806B,以及两个可将来自 4 通道 DAC 的 I/Q 输出上变频为射频载波的 TRF3705。DAC34H84 是一款四通道、超低功耗 16 位 1.25GSPS DAC,最大输入模式率为 625MSPS/DAC。TRF3705 是高性能复数射频调制器,输出范围为 300MHz 至 4GHz。LMK04806B 是低噪声时钟发生器和抖动消除器,适用于低于 150fs rms 抖动量和高达 1300MHz 的输出频率,以全速率为 DAC34SH84 计时。评估模块可以与 TSW1400/TSW1406/TSW3100 图形发生器结合使用,用于执行大量测试步骤。TSW1400/TSW3100 可以与 DAC34H84 结合使用以实现高达 1.25GSPS 的图形,而 TSW1406 则用于高达 1GSPS 的低成本简单图形。除了向 DAC34H84 提供高品质、低抖动的 DAC 采样时钟,LMK04806B 还向 TSW1400/TSW1406/TSW3100 提供作为 FPGA 参考时钟的 FPGA 时钟。发射射频信号路径还包括放大器和可编程衰减器。

|

|

特性

- 包含用于时钟生成和抖动消除的 LMK04806B

- 直接连接到 TSW1400/TSW1406/TSW3100 TSW1406 信号发生器

- 发送器(DAC34H84 四路 DAC 和两个 TRF3705 IQ 调制器)对射频输出具有综合测试能力

- 具有完整功能 GUI 的软件支持,以确保轻松测试和原型设计

- FMC-DAC-Adapter 卡兼容连接 Xilinx FPGA EVM 上提供的 FMC 互连接头

- 直接兼容 Altera FPGA EVM 上的 HSMC 接头

|

|

TSW30SH84EVM 评估模块

Texas Instruments TSW30SH84EVM 评估模块为电路板,可允许系统设计人员借助 LMK04806B 低噪声时钟发生器/抖动消除器,评估 TI 发射信号链的总性能。作为易于使用的完整射频发射解决方案,TSW30SH84EVM 包含用于为 DAC3484 数模转换器 (DAC) 提供计时的 LMK04800,以及两个可将来自 4 通道 DAC 的 I/Q 输出上变频为射频载波的 TRF3705。DAC34SH84 是一款四通道、超低功耗 16 位 1.5GSPS DAC,最大输入模式率为 750MSPS/DAC。TRF3705 是高性能复数射频调制器,输出范围为 300MHz 至 4GHz。LMK04800 是低噪声时钟发生器和抖动消除器,适用于低于 150fs rms 抖动量和高达 1500MHz 的输出频率,以全速率为 DAC34SH84 计时。评估模块可以与 TSW1400/TSW1406/TSW3100 图形发生器结合使用,用于执行大量测试步骤。TSW1400 生成一些测图形,通过运行速度达 1.5GSPS 的 LVDS 端口反馈至 DAC34SH84。TSW3100 可以用于实现高达 1.25GSPS 的图形,而 TSW1406 则用于高达 1GSPS 的低成本简单图形。除了向 DAC34SH84 提供高品质、低抖动的 DAC 采样时钟,LMK04800 还向 TSW1400/TSW1406/TSW3100 提供作为 FPGA 参考时钟的 FPGA 时钟。发射射频信号路径还包括放大器和可编程衰减器。

|

|

特性

- 包含用于时钟生成和抖动消除的 LMK04800

- 直接连接到 TSW1400/TSW1406/TSW3100 信号发生器

- 发送器具有综合测试能力;DAC34H84 四路 DAC 和两个 TRF3705 IQ 调制器具有射频输出

- 具有完整功能 GUI 的软件支持,以确保轻松测试和原型设计

- FMC-DAC-Adapter 卡兼容连接 Xilinx FPGA EVM 上提供的 FMC 互连接头

- 直接兼容 Altera FPGA EVM 上的 HSMC 接头

|

|

|

|

TSW4806 评估模块 (EVM)

Texas Instruments TSW4806 评估模块 (EVM) 使用 LMK04806 双 PLL 时钟抖动清除器和发生器,提供低成本、低噪声、便携式时钟解决方案,结合 TI 高速数据转换器评估模块使用。结合附带的基于Labview的图形用户界面(GUI),此模块是一款全面的计时工具。当结合其他低成本 TI 评估工具使用时,它们提供从 ADC 评估模块中采集和评估数据样本并向 DAC EVM 生成测试图形的完备系统。评估模块的板载 EEPROM 配有多项预编程寄存器设置,因此该板可以在不需要使用 GUI 界面时即可开始运行。EEPROM 提供最多保存八个自定义 LMK04806 配置设置所需的内存。

特性

- 多模:双 PLL、单 PLL 和时钟分配

- 双环路 PLLatinum™ PLL 架构

- 50% 的占空比输出除数,1至1045(偶数和奇数)

- LVPECL、LVDS 或 LVCMOS 可编程输出

- 精确度数字延迟,固定或动态可调

- 25 ps 步进模拟延迟控制

- 双差分输出

- 4 个单端输出

- 0 延迟模式

- 板载 10MHz 基准振荡器

- 用户友好型图形界面 (GUI)

|

|

|

|

|

|

|

发布日期: 2015-12-14

| 更新日期: 2024-01-15