当器件上PRE和CLR无效(高电平)时,满足设置时间要求的数据 (D) 输入处的数据在时钟 (CLK) 脉冲的正向边沿上传送到输出 (Q, Q)。时钟触发在某一电平下发展,并且与输入时钟 (CLK) 信号的上升时间没有直接关系。在遵守保持时间间隔的前提下,可以更改数据 (D) 输入端的数据,而不会影响输出端的电平。SN74HCS74-Q1器件符合汽车应用类AEC-Q100认证。

特性

- 宽工作电压范围:2V至6V

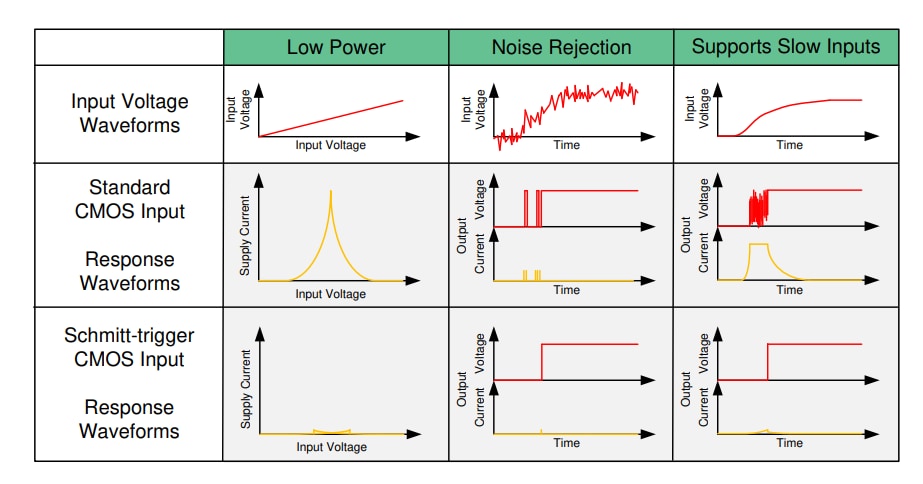

- 施密特触发器输入允许缓慢或嘈杂的输入信号

- 低功耗

- 典型ICC为100nA

- 典型输入漏电流:±100nA

- 输出驱动:±7.8mA (5V)

应用

- 将瞬时开关转换为拨动开关

- 在控制器复位期间保持信号

- 输入缓慢边沿速率信号

- 在嘈杂环境中运行

- 将时钟信号除以2

施密特触发器输入图表的益处

功能图

其他资源

发布日期: 2019-07-30

| 更新日期: 2023-10-11