Texas Instruments LMK04208超低噪声时钟抖动清除器

Texas Instruments LMK04208超低噪声时钟抖动清除器是一款高性能时钟调理器,具有卓越的时钟抖动清除、生成和分配功能 该器件包括众多高级功能,能够充分满足新一代系统要求。 双环 PLLatinum™架构利用低噪声VCXO模块能够实现111fs RMS抖动(12kHz至20MHz)或采用低成本外部晶振及变容二极管实现低于200fs的RMS抖动(12kHz至20MHz)。 双环架构由两个高性能锁相环(PLL)、一个低噪声晶体振荡器电路以及一个高性能压控振荡器(VCO)构成。 第1个PLL (PLL1)提供低噪声抖动清除器功能,而第2个PLL (PLL2)则执行时钟生成功能。特性

- Ultra-low RMS jitter performance

- 111fs, RMS jitter (12kHz to 20MHz)

- 123fs, RMS jitter (100Hz to 20MHz)

- Dual loop PLLatinum™ PLL architecture

- PLL1:

- Integrated low-noise crystal oscillator circuit

- Holdover mode when input clocks are lost

- Automatic or manual triggering/recovery

- PLL2:

- Normalized PLL noise floor of –227dBc/Hz

- Phase detector rate of up to 155MHz

- OSCin frequency-doubler

- Integrated low-noise VCO or external VCO mode

- Two redundant input clocks with LOS

- Automatic and manual switch-over modes

- 50% duty cycle output divides, 1 to 1045 (even and odd)

- Six LVPECL, LVDS, or LVCMOS programmable outputs

- Digital delay (fixed or dynamically adjustable)

- 25ps step analog delay control

- Seven differential outputs, up to 14 single-ended

- Up to six VCXO/crystal buffered outputs

- Clock rates of up to 1536MHz

- 0-delay mode

- Three default clock outputs at power-up

- Multi-mode: dual PLL, single PLL, and clock distribution

- –40°C to +85°C industrial temperature range

- 3.15V to 3.45V operation

- 64-Pin WQFN package (9mm × 9mm × 0.8mm)

应用

- Data converter clocking

- Wireless infrastructure

- Networking, SONET/SDH, DSLAM

- Medical, video, military, and aerospace

- Test and measurement

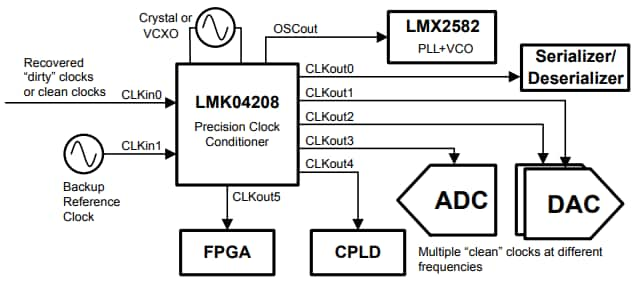

Simplified Schematic

发布日期: 2016-10-27

| 更新日期: 2022-03-11